## ML620Q503H/Q504H ユーザーズマニュアル

初版 発行日 2015 年 8 月 31 日

#### ご注意

- 1) 本資料の記載内容は改良などのため予告なく変更することがあります。

- 2) ラピスセミコンダクタは常に品質・信頼性の向上に取り組んでおりますが、半導体製品は種々の要因で故障・誤作動する可能性があります。

- 万が一、本製品が故障・誤作動した場合であっても、その影響により人身事故、火災損害等が起こらないようご使用機器でのディレーティング、冗長設計、延焼防止、バックアップ、フェイルセーフ等の安全確保をお願いします。 定格を超えたご使用や使用上の注意書が守られていない場合、いかなる責任もラピスセミコンダクタは負うものではありません。

- 3) 本資料に記載されております応用回路例やその定数などの情報につきましては、本製品の標準的な動作や使い 方を説明するものです。したがいまして、量産設計をされる場合には、外部諸条件を考慮していただきますようお 願いいたします。

- 4) 本資料に記載されております技術情報は、本製品の代表的動作および応用回路例などを示したものであり、それをもって、当該技術情報に関するラピスセミコンダクタまたは第三者の知的財産権その他の権利を許諾するものではありません。したがいまして、上記技術情報の使用に起因して第三者の権利にかかわる紛争が発生した場合、ラピスセミコンダクタはその責任を負うものではありません。

- 5) 本製品は、一般的な電子機器(AV機器、OA機器、通信機器、家電製品、アミューズメント機器など)および本資料に明示した用途への使用を意図しています。

- 6) 本資料に掲載されております製品は、耐放射線設計はなされておりません。

- 7) 本製品を下記のような特に高い信頼性が要求される機器等に使用される際には、ラピスセミコンダクタへ必ずご連絡の上、承諾を得てください。

- ・輸送機器(車載、船舶、鉄道など)、幹線用通信機器、交通信号機器、防災・防犯装置、安全確保のための装置、医療機器、サーバー、太陽電池、送電システム

- 8) 本製品を極めて高い信頼性を要求される下記のような機器等には、使用しないでください。

- ·航空宇宙機器、原子力制御機器、海底中継機器

- 9) 本資料の記載に従わないために生じたいかなる事故、損害もラピスセミコンダクタはその責任を負うものではありません。

- 10) 本資料に記載されております情報は、正確を期すため慎重に作成したものですが、万が一、当該情報の誤り・誤植に起因する損害がお客様に生じた場合においても、ラピスセミコンダクタはその責任を負うものではありません。

- 11) 本製品のご使用に際しては、RoHS 指令など適用される環境関連法令を遵守の上ご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、ラピスセミコンダクタは一切の責任を負いません。本製品のRoHS 適合性などの詳細につきましては、セールス・オフィスまでお問合せください。

- 12) 本製品および本資料に記載の技術を輸出又は国外へ提供する際には、「外国為替及び外国貿易法」、「米国輸出管理規則」など適用される輸出関連法令を遵守し、それらの定めにしたがって必要な手続を行ってください。

- 13) 本資料の一部または全部をラピスセミコンダクタの許可なく、転載・複写することを堅くお断りします。

Copyright 2015 LAPIS Semiconductor Co., Ltd.

## ラピスセミコンダクタ株式会社

〒222-8575 神奈川県横浜市港北区新横浜 2-4-8 http://www.lapis-semi.com

FJUL620Q504H 1

### はじめに

本ユーザーズマニュアルでは、16ビットマイクロコントローラ ML620Q503H/Q504H のハードウェアの動作説明が記述されています。

本書のほかに以下に示すマニュアルが用意されておりますので、必要に応じてあわせてお読み下さい。

- nX-U16/100 コア インストラクションマニュアル nX-U16/100 コアの基本アーキテクチャおよび各命令の説明

- MACU8 アセンブラパッケージ ユーザーズマニュアル リロケータブルアセンブラ、リンカ、ライブラリアン、オブジェクトコンバータの操作方法の説明およびアセ ンブリ言語仕様の説明

- CCU8 ユーザーズマニュアル コンパイラの操作方法の説明

- CCU8 プログラミングガイド プログラミング方法の説明

- CCU8 ランゲージリファレンス CCU8 の言語仕様の説明

- DTU8 デバッガ ユーザーズマニュアル デバッガ DTU8 の操作方法の説明

- IDEU8 ユーザーズマニュアル 統合化開発環境 IDEU8 の操作方法の説明

- uEASE ユーザーズマニュアル オンチップデバッグツール uEASE の説明

- uEASE ターゲット接続補足マニュアル uEASE と ML620Q503H/Q504H の接続方法の説明

- FWuEASE フラッシュライタ ホストプログラム ユーザーズマニュアル フラッシュライタ ホストプログラム FWuEASE の説明

FJUL620Q504H 2

## 表記法

| 分 類  | 表記法                                                                                                 | 説 明                                                                                                                                                     |

|------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| ● 数値 | xxh, xxH<br>xxb                                                                                     | 16 進数を表します。<br>2 進数を表します。                                                                                                                               |

| ● 単位 | ワード, W<br>バイト, B<br>ニブル, N<br>メガ, M<br>キロ, K<br>キロ, k<br>ミリ, m<br>マイクロ, μ<br>ナノ, n<br>セカンド, s (小文字) | 1 ワード = 16 ビット 1 バイト = 8 ビット 1 ニブル=4 ビット 10 <sup>6</sup> 2 <sup>10</sup> =1024 10 <sup>3</sup> =1000 10 <sup>-3</sup> 10 <sup>-6</sup> 10 <sup>-9</sup> |

● 用語 "H"レベル:電圧の高い側の信号レベルで、電気的特性で規定された V<sub>IH</sub>、V<sub>OH</sub>の 電圧レベルを示します。

"L" レベル: 電圧の低い側の信号レベルで、電気的特性で規定された  $V_{IL}$ 、 $V_{OL}$  の電圧レベルを示します。

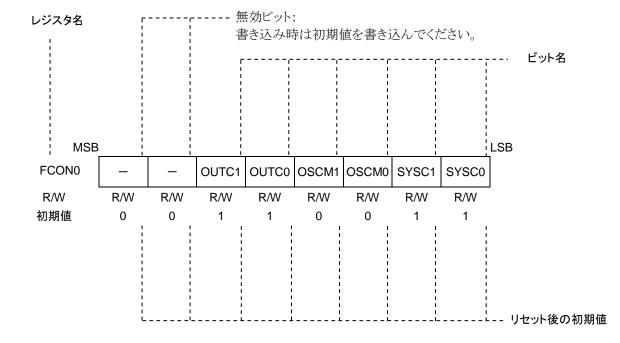

#### ● レジスタ説明図

R/W: 読み書き属性を表します。R は読み出し可能、W は書き込み可能、R/W は読み書き可能です。

MSB: 8 ビットのレジスタ(メモリ)の最上位ビット LSB: 8 ビットのレジスタ(メモリ)の最下位ビット

FJUL620Q504H 3

## 第1章 概要

| 1. 概要                                     | 1-1  |

|-------------------------------------------|------|

| 1.1 特長                                    | 1-1  |

| 1.2 機能ブロック構成                              |      |

| 1.2.1 ML620Q503H/Q504H ブロック図              |      |

| 1.3 端子                                    |      |

| 1.3.1 端子配置                                |      |

| 1.3.1.1 ML620Q503H/Q504H TQFP パッケージの端子配置図 |      |

| 1.3.2 端子一覧                                |      |

| 1.3.2.1 ML620Q503H/Q504H TQFP パッケージの端子一覧  |      |

| 1.3.3 端子説明                                |      |

| 1.3.4 未使用端子の処理                            | 1-11 |

| 第2章 CPU とメモリ空間                            |      |

|                                           | 2-1  |

| 2.1 概要                                    |      |

| 2.1.1 特長                                  |      |

| 2.1.2 SB/RB 命令実行時の注意事項                    |      |

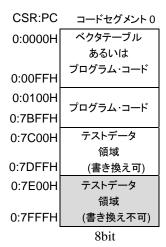

| 2.2 プログラム・メモリ空間                           |      |

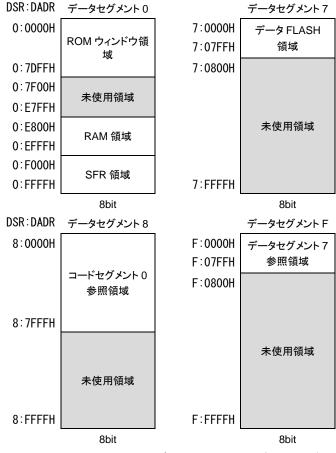

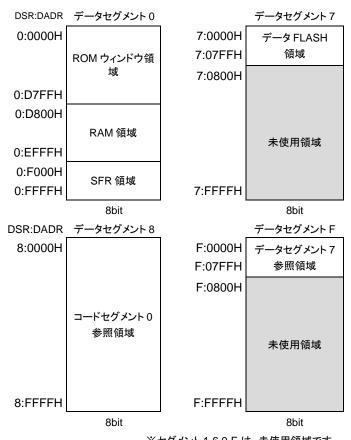

| 2.3 データ・メモリ空間                             |      |

| 2.4 命令長                                   | 2-4  |

| 2.5 データタイプ                                | 2-4  |

| 2.6 レジスタ説明                                | 2-4  |

| 2.6.1 レジスター覧                              |      |

| 2.6.2 データセグメントレジスタ (DSR)                  |      |

| 2.7 乗除算コプロセッサ                             |      |

| 2.7.1 概要                                  |      |

| 2.7.2 レジスター覧                              |      |

| 2.7.2.1 A,B,C,D レジスタ (CR0~CR7)            |      |

| 2.7.2.2 演算モードレジスタ (CR8)                   |      |

| 2.7.2.3 演算ステータスレジスタ (CR9)                 |      |

| 2.7.2.4 コプロ ID レジスタ(CR15)<br>2.7.3 動作説明   |      |

| 2.7.3 動作説明                                | ∠-⊱  |

|                                           |      |

| 笠 2 辛 . ロ し… し 総分:                        |      |

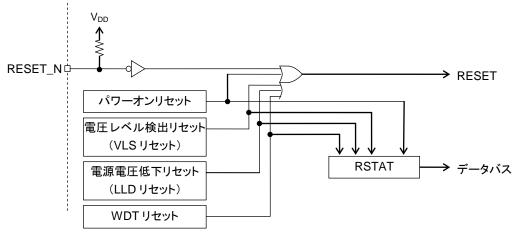

| <u>第3章 リセット機能</u>                         |      |

| 3. リセット機能                                 |      |

| 3.1 概要                                    |      |

| 3.1.1 特長                                  |      |

| 3.1.2 構成                                  |      |

| 3.1.3 端子一覧                                |      |

| 3.2 レジスタ説明                                |      |

| 3.2.1 レジスター覧                              | 3-2  |

| 3.2.2 リセットステーダスレンスダ (RSTAT)               |      |

| 3.3.1 リセット要因                              |      |

| 3.3.2 システムリセットモードの動作                      |      |

|                                           |      |

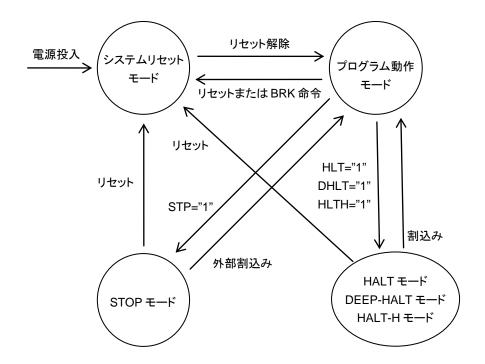

## 第4章 パワーマネジメント

| 4. パワーマネジメント                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 4.1 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-1                                                             |

| 4.1.1 特長                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-1                                                             |

| 4.1.2 構成                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-1                                                             |

| 4.2 レジスタ説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-2                                                             |

| 4.2.1 レジスター覧                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-2                                                             |

| 4.2.2 ストップコードアクセプタ (STPACP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-3                                                             |

| 4.2.3 スタンバイコントロールレジスタ (SBYCON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-4                                                             |

| 4.2.4 ブロックコントロールレジスタ 01 (BLKCON01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 |

| 4.2.5 ブロックコントロールレジスタ 23 (BLKCON23)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 |

| 4.2.6 ブロックコントロールレジスタ 45(BLKCON45)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                 |

| 4.3 動作説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                 |

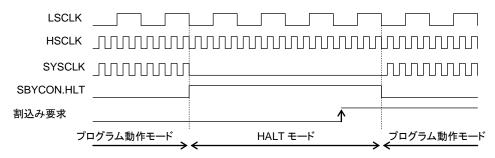

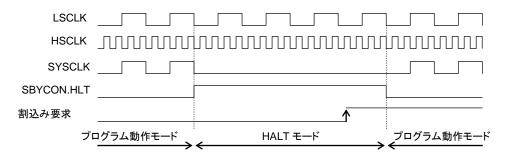

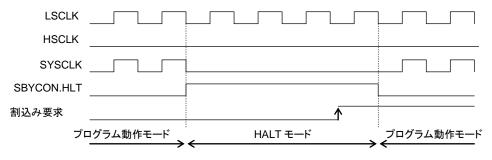

| 4.3.1 HALT モード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |

| 4.3.1.1 HALT モード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                 |

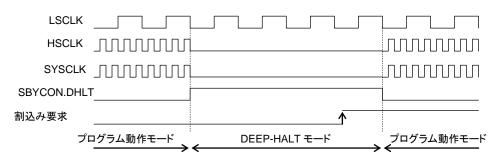

| 4.3.1.2 DEEP-HALT モード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                 |

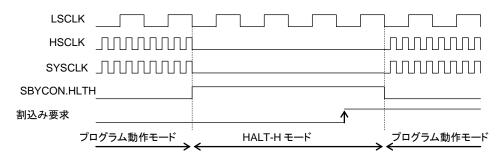

| 4.3.1.3 HALT-H モード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                 |

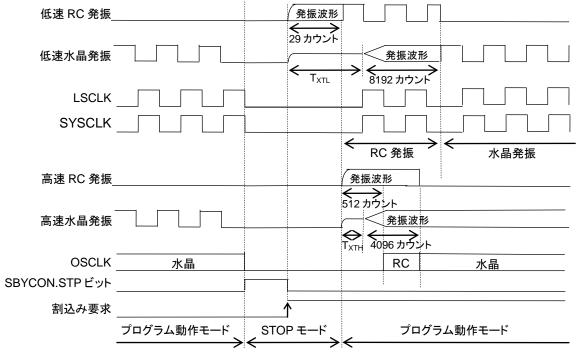

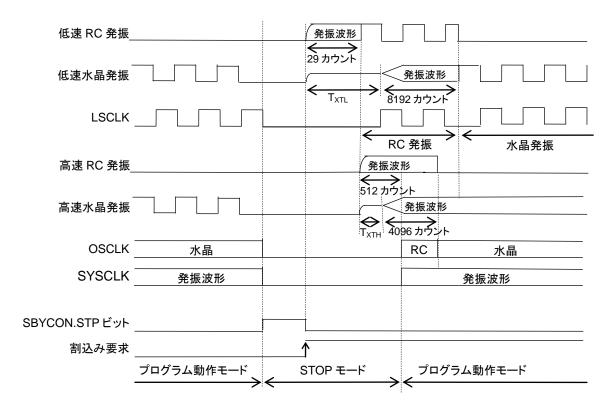

| 4.3.2 STOP モード                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |

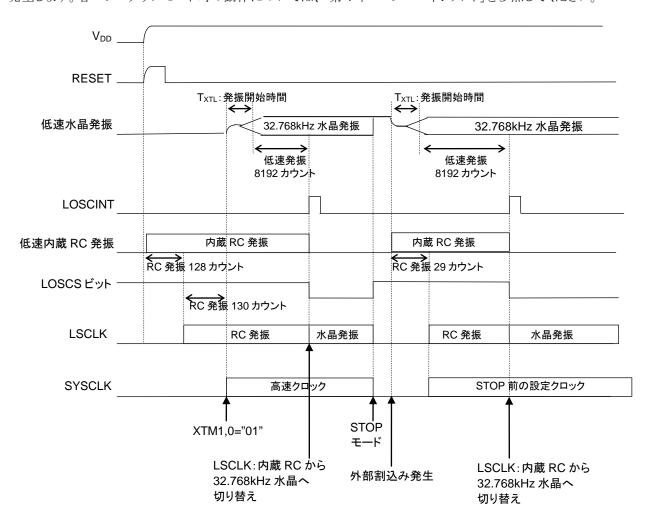

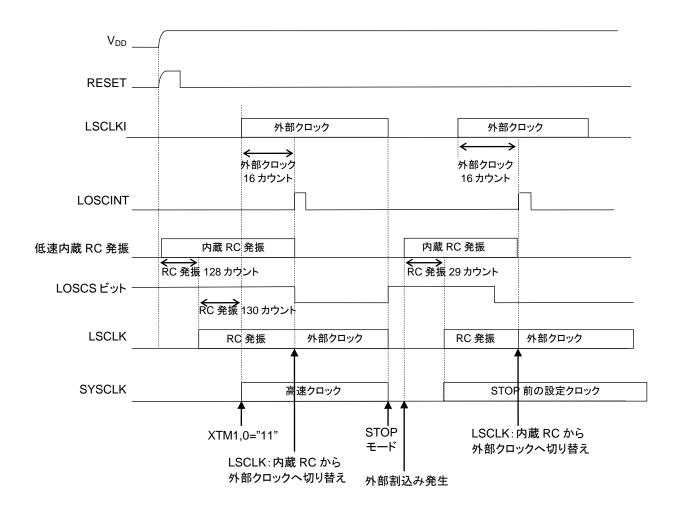

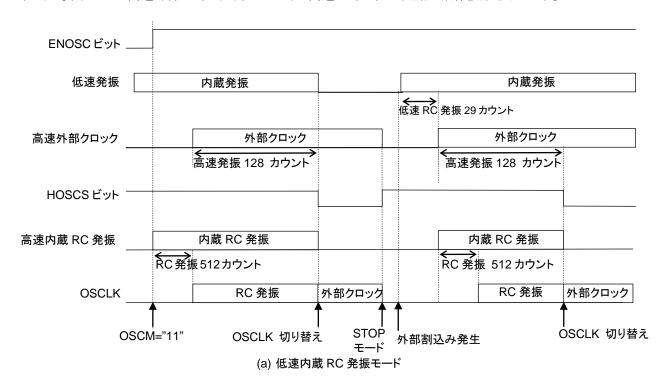

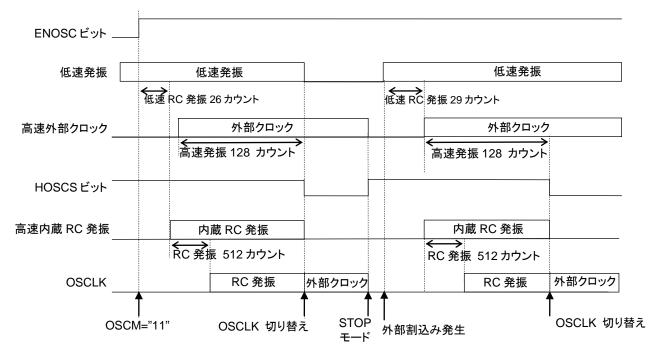

| 4.3.2.1 低速クロックの発振停止と再開タイミング                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                 |

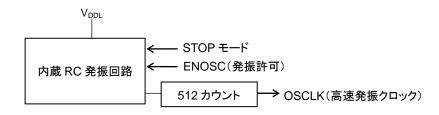

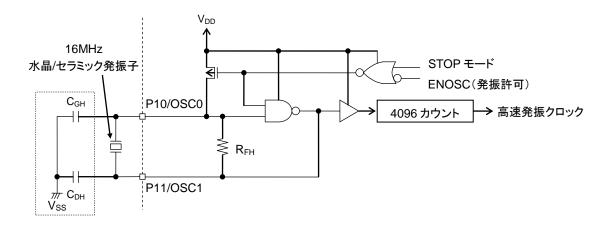

| 4.3.2.2 高速クロックの発振停止と再開タイミング                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                 |

| 4.3.2.3 STOP/HALT/DEEP-HALT/HALT-H モードからの復帰動作についての注意事項                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                               |

| 4.3.3 STOP/HALT/DEEP-HALT/HALT-H モード時の各機能の動作                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |

| 4.3.4 ブロック制御機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-17                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                 |

| 5. 割込み                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                 |

| 5.1 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1                                                             |

| 5.1 概要<br>5.1.1 特長                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-1<br>5-1                                                      |

| 5.1 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-1<br>5-1                                               |

| 5.1 概要<br>5.1.1 特長<br>5.1.2 構成                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-1<br>5-1<br>5-1<br>5-2                                        |

| 5.1 概要<br>5.1.1 特長<br>5.1.2 構成<br>5.2 レジスタ説明<br>5.2.1 レジスター覧                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-1<br>5-1<br>5-1<br>5-2                                        |

| 5.1 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-1<br>5-1<br>5-2<br>5-2                                 |

| 5.1 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1<br>5-1<br>5-1<br>5-2<br>5-2<br>5-4                          |

| 5.1 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-15-15-25-45-65-8                                              |

| 5.1 概要         5.1.1 特長         5.1.2 構成         5.2 レジスタ説明         5.2.1 レジスター覧         5.2.2 割込み許可レジスタ 01 (IE01)         5.2.3 割込み許可レジスタ 23 (IE23)         5.2.4 割込み許可レジスタ 45 (IE45)                                                                                                                                                                                                                                                                                                                                                                                                              | 5-15-15-25-45-65-8                                              |

| 5.1 概要<br>5.1.1 特長<br>5.1.2 構成<br>5.2 レジスタ説明<br>5.2.1 レジスター覧<br>5.2.2 割込み許可レジスタ 01 (IE01)<br>5.2.3 割込み許可レジスタ 23 (IE23)<br>5.2.4 割込み許可レジスタ 45 (IE45)<br>5.2.5 割込み許可レジスタ 67 (IE67)<br>5.2.6 割込み要求レジスタ 01 (IRQ01)<br>5.2.7 割込み要求レジスタ 23 (IRQ23)                                                                                                                                                                                                                                                                                                                                                        | 5-15-15-25-45-65-15-105-12                                      |

| 5.1 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-15-15-25-45-65-85-105-12                                      |

| 5.1 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-15-15-25-45-65-105-125-145-16                                 |

| 5.1 概要<br>5.1.1 特長<br>5.1.2 構成<br>5.2 レジスタ説明<br>5.2.1 レジスター覧<br>5.2.2 割込み許可レジスタ 01 (IE01)<br>5.2.3 割込み許可レジスタ 23 (IE23)<br>5.2.4 割込み許可レジスタ 45 (IE45)<br>5.2.5 割込み許可レジスタ 67 (IE67)<br>5.2.6 割込み要求レジスタ 01 (IRQ01)<br>5.2.7 割込み要求レジスタ 23 (IRQ23)<br>5.2.8 割込み要求レジスタ 45 (IRQ45)<br>5.2.9 割込み要求レジスタ 67 (IRQ67)<br>5.2.10 割込みレベル制御イネーブルレジスタ (ILEN)                                                                                                                                                                                                                                                         | 5-15-15-25-45-65-105-125-145-165-19                             |

| 5.1 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-15-15-25-45-65-105-125-145-165-195-21                         |

| 5.1 概要 5.1.1 特長 5.1.2 構成 5.2 レジスタ説明 5.2.1 レジスター覧 5.2.2 割込み許可レジスタ 01 (IE01) 5.2.3 割込み許可レジスタ 23 (IE23) 5.2.4 割込み許可レジスタ 45 (IE45) 5.2.5 割込み許可レジスタ 67 (IE67) 5.2.6 割込み要求レジスタ 01 (IRQ01) 5.2.7 割込み要求レジスタ 23 (IRQ23) 5.2.8 割込み要求レジスタ 45 (IRQ45) 5.2.9 割込み要求レジスタ 67 (IRQ67) 5.2.10 割込みサベルレジスタ (ILEN) 5.2.11 現割込み要求レベルレジスタ (CIL) 5.2.12 割込みレベル制御レジスタ 1 (ILC1)                                                                                                                                                                                                                                               | 5-15-15-25-45-65-105-125-145-195-215-22                         |

| 5.1 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-15-15-25-45-65-105-145-145-165-195-215-245-24                 |

| 5.1 概要 5.1.1 特長 5.1.2 構成 5.2 レジスタ説明 5.2.1 レジスター覧 5.2.2 割込み許可レジスタ 01 (IE01) 5.2.3 割込み許可レジスタ 23 (IE23) 5.2.4 割込み許可レジスタ 45 (IE45) 5.2.5 割込み許可レジスタ 67 (IE67) 5.2.6 割込み要求レジスタ 01 (IRQ01) 5.2.7 割込み要求レジスタ 23 (IRQ23) 5.2.8 割込み要求レジスタ 45 (IRQ45) 5.2.9 割込み要求レジスタ 67 (IRQ67) 5.2.10 割込みレベル制御イネーブルレジスタ (ILEN) 5.2.11 現割込み要求レベルレジスタ (CIL) 5.2.12 割込みレベル制御レジスタ 1 (ILC1) 5.2.13 割込みレベル制御レジスタ 2 (ILC2) 5.2.14 割込みレベル制御レジスタ 3 (ILC3)                                                                                                                                                                              | 5-15-15-25-65-85-105-145-165-195-215-225-245-265-28             |

| 5.1 概要 5.1.1 特長 5.1.2 構成 5.2 レジスタ説明 5.2.1 レジスター覧 5.2.2 割込み許可レジスタ 01 (IE01) 5.2.3 割込み許可レジスタ 23 (IE23) 5.2.4 割込み許可レジスタ 45 (IE45) 5.2.5 割込み許可レジスタ 67 (IE67) 5.2.6 割込み要求レジスタ 01 (IRQ01) 5.2.7 割込み要求レジスタ 23 (IRQ23) 5.2.8 割込み要求レジスタ 45 (IRQ45) 5.2.9 割込み要求レジスタ 67 (IRQ67) 5.2.10 割込みレベル制御イネーブルレジスタ (ILEN) 5.2.11 現割込み要求レベルレジスタ (CIL) 5.2.12 割込みレベル制御レジスタ 1 (ILC1) 5.2.13 割込みレベル制御レジスタ 2 (ILC2) 5.2.14 割込みレベル制御レジスタ 3 (ILC3) 5.2.15 割込みレベル制御レジスタ 4 (ILC4)                                                                                                                                                 | 5-15-15-25-45-65-105-125-145-165-195-215-245-285-28             |

| 5.1 概要 5.1.1 特長 5.1.2 構成 5.2 レジスタ説明 5.2.1 レジスター覧 5.2.2 割込み許可レジスタ 01 (IE01) 5.2.3 割込み許可レジスタ 23 (IE23) 5.2.4 割込み許可レジスタ 45 (IE45) 5.2.5 割込み許可レジスタ 67 (IE67) 5.2.6 割込み要求レジスタ 01 (IRQ01) 5.2.7 割込み要求レジスタ 23 (IRQ23) 5.2.8 割込み要求レジスタ 45 (IRQ45) 5.2.9 割込み要求レジスタ 67 (IRQ67) 5.2.10 割込みレベル制御イネーブルレジスタ (ILEN) 5.2.11 現割込み要求レベルレジスタ (CIL) 5.2.12 割込みレベル制御レジスタ 1 (ILC1) 5.2.13 割込みレベル制御レジスタ 3 (ILC3) 5.2.14 割込みレベル制御レジスタ 4 (ILC4) 5.2.15 割込みレベル制御レジスタ 4 (ILC4) 5.2.16 割込みレベル制御レジスタ 5 (ILC5)                                                                                                                    | 5-15-15-25-65-85-105-145-165-195-215-245-295-29                 |

| 5.1 概要 5.1.1 特長 5.1.2 構成 5.2 レジスタ説明 5.2.1 レジスター覧 5.2.2 割込み許可レジスタ 01 (IE01) 5.2.3 割込み許可レジスタ 23 (IE23) 5.2.4 割込み許可レジスタ 45 (IE45) 5.2.5 割込み許可レジスタ 67 (IE67) 5.2.6 割込み要求レジスタ 30 (IRQ01) 5.2.7 割込み要求レジスタ 23 (IRQ23) 5.2.8 割込み要求レジスタ 45 (IRQ45) 5.2.9 割込み要求レジスタ 45 (IRQ45) 5.2.10 割込みレベル制御イネーブルレジスタ (ILEN) 5.2.11 現割込み要求レベルレジスタ (CIL) 5.2.12 割込みレベル制御レジスタ 1 (ILC1) 5.2.13 割込みレベル制御レジスタ 1 (ILC1) 5.2.14 割込みレベル制御レジスタ 3 (ILC2) 5.2.15 割込みレベル制御レジスタ 4 (ILC2) 5.2.16 割込みレベル制御レジスタ 4 (ILC4) 5.2.16 割込みレベル制御レジスタ 5 (ILC5) 5.2.17 割込みレベル制御レジスタ 5 (ILC5) 5.2.17 割込みレベル制御レジスタ 6 (ILC6)                             | 5-15-15-25-65-85-105-125-145-155-155-215-215-225-245-285-315-33 |

| 5.1 概要<br>5.1.1 特長<br>5.1.2 構成<br>5.2 レジスター覧<br>5.2.1 レジスター覧<br>5.2.2 割込み許可レジスタ 01 (IE01)<br>5.2.3 割込み許可レジスタ 23 (IE23)<br>5.2.4 割込み許可レジスタ 45 (IE45)<br>5.2.5 割込み許可レジスタ 67 (IE67)<br>5.2.6 割込み要求レジスタ 01 (IRQ01)<br>5.2.7 割込み要求レジスタ 23 (IRQ23)<br>5.2.8 割込み要求レジスタ 45 (IRQ45)<br>5.2.9 割込み要求レジスタ 67 (IRQ67)<br>5.2.10 割込みレベル制御イネーブルレジスタ (ILEN)<br>5.2.11 現割込み要求レベルレジスタ (CIL)<br>5.2.12 割込みレベル制御レジスタ 1 (ILC1)<br>5.2.13 割込みレベル制御レジスタ 2 (ILC2)<br>5.2.14 割込みレベル制御レジスタ 3 (ILC3)<br>5.2.15 割込みレベル制御レジスタ 4 (ILC4)<br>5.2.16 割込みレベル制御レジスタ (ILC4)<br>5.2.17 割込みレベル制御レジスタ (ILC5)<br>5.2.17 割込みレベル制御レジスタ (ILC5) | 5-15-15-25-65-65-105-125-145-165-195-215-225-245-285-295-335-35 |

| 5.1 概要 5.1.1 特長 5.1.2 構成 5.2 レジスタ説明 5.2.1 レジスター覧 5.2.2 割込み許可レジスタ 01 (IE01) 5.2.3 割込み許可レジスタ 23 (IE23) 5.2.4 割込み許可レジスタ 45 (IE45) 5.2.5 割込み許可レジスタ 67 (IE67) 5.2.6 割込み要求レジスタ 30 (IRQ01) 5.2.7 割込み要求レジスタ 23 (IRQ23) 5.2.8 割込み要求レジスタ 45 (IRQ45) 5.2.9 割込み要求レジスタ 45 (IRQ45) 5.2.10 割込みレベル制御イネーブルレジスタ (ILEN) 5.2.11 現割込み要求レベルレジスタ (CIL) 5.2.12 割込みレベル制御レジスタ 1 (ILC1) 5.2.13 割込みレベル制御レジスタ 1 (ILC1) 5.2.14 割込みレベル制御レジスタ 3 (ILC2) 5.2.15 割込みレベル制御レジスタ 4 (ILC2) 5.2.16 割込みレベル制御レジスタ 4 (ILC4) 5.2.16 割込みレベル制御レジスタ 5 (ILC5) 5.2.17 割込みレベル制御レジスタ 5 (ILC5)                                                          | 5-15-15-25-65-85-105-145-145-155-195-215-215-245-265-285-355-35 |

| 5.2.21 外部割込み 01 選択レジスタ (EXIO1SEL) | 5-38 |

|-----------------------------------|------|

| 5.2.22 外部割込み 23 選択レジスタ (EXI23SEL) | 5-39 |

| 5.2.23 外部割込み 45 選択レジスタ (EXI45SEL) | 5-40 |

| 5.2.24 外部割込み 67 選択レジスタ (EXI67SEL) | 5-41 |

| 5.3 動作説明                          | 5-42 |

| 5.3.1 割込み要因                       | 5-42 |

| 5.3.2 マスカブル割込み処理                  | 5-44 |

| 5.3.3 ノンマスカブル割込み処理                | 5-44 |

| 5.3.4 ソフトウェア割込み処理                 | 5-44 |

| 5.3.5 割込みルーチンでの注意事項               | 5-45 |

| 5.3.6 割込みレベル制御有効時の割込み処理           | 5-48 |

| 5.3.7 フローチャート(割込みレベル制御有効時)        | 5-49 |

| 5.3.8 割込み禁止状態                     | 5-51 |

| 5.3.9 外部割込み                       | 5-52 |

|                                   |      |

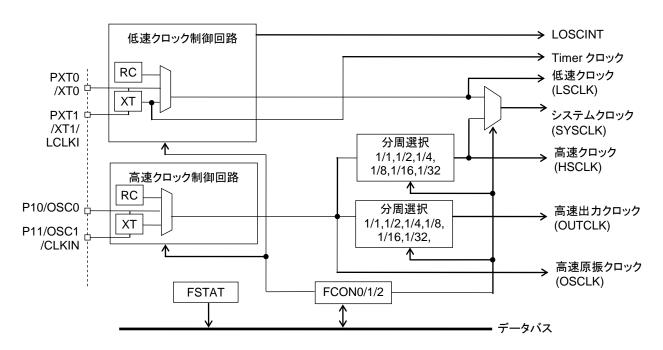

| 第6章 クロック発生回路                      |      |

|                                   |      |

| 6.1 概要                            |      |

| 6.1.1 特長                          |      |

| 6.1.2 構成                          |      |

| 6.1.3 端子一覧                        |      |

| 6.1.4 クロック構成図                     |      |

| 6.2 レジスタ説明                        |      |

| 6.2.1 レジスター覧                      |      |

| 6.2.2 周波数コントロールレジスタ 01(FCON01)    |      |

| 6.2.3 周波数コントロールレジスタ 23(FCON23)    |      |

| 6.2.4 周波数ステータスレジスタ (FSTAT)        |      |

| 6.3 動作説明                          |      |

| 6.3.1 低速クロック                      |      |

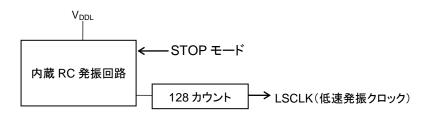

| 6.3.1.1 低速内蔵 RC 発振モード             |      |

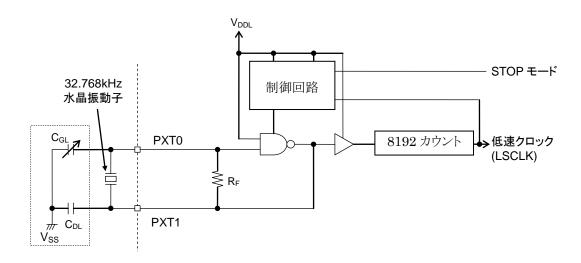

| 6.3.1.2 低速水晶発振モード                 |      |

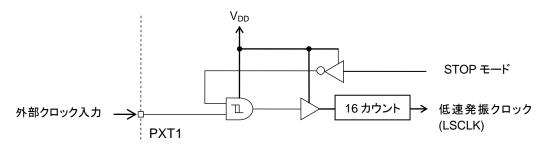

| 6.3.1.3 低速外部クロック入力モード             |      |

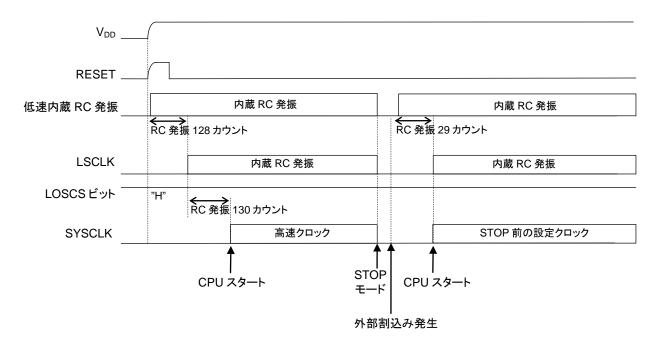

| 6.3.1.4 低速内蔵 RC 発振モードの動作          |      |

| 6.3.1.5 低速水晶発振モードの動作              |      |

| 6.3.1.6 低速外部クロックモードの動作            |      |

| 6.3.2 高速クロック                      |      |

| 6.3.2.1 内蔵 RC 発振モード               |      |

| 6.3.2.2 水晶/セラミック発振モード             |      |

| 6.3.2.3 高速外部クロック入力モード             |      |

| 6.3.2.4 内蔵 RC 発振モードの動作            |      |

| 6.3.2.5 水晶/セラミック発振モードの動作          |      |

| 6.3.2.6 高速外部クロックモードの動作            |      |

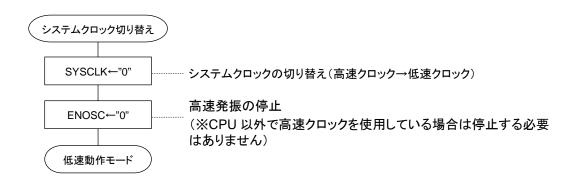

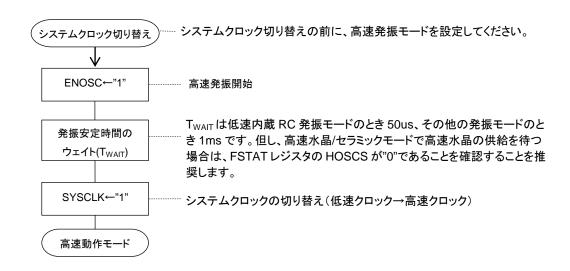

| 6.3.3 システムクロック切り替え                |      |

| 6.3.4 低速発振クロック切り替え割込み             | 6-23 |

| 第7章 タイムベースカウンタ                    |      |

| 7. タイムベースカウンタ                     | 7-1  |

| 7.1 概要                            | 7-1  |

| 7.1.1 特長                          |      |

| 7.1.2 構成                          | 7-1  |

| 7          | 7.2 レジス | 夕説明                                                                                       | 7-2  |

|------------|---------|-------------------------------------------------------------------------------------------|------|

|            | 7.2.1   | レジスター覧                                                                                    | 7-2  |

|            |         | 低速タイムベースカウンタレジスタ (LTBR)                                                                   |      |

|            |         | 低速タイムベースカウンタ周波数補正レジスタ(LTBADJ)                                                             |      |

|            |         | 低速タイムベースカウンタ割込み選択レジスタ (LTBINT)                                                            |      |

| 7          | 7.3 動作詞 | 兑明                                                                                        | 7-7  |

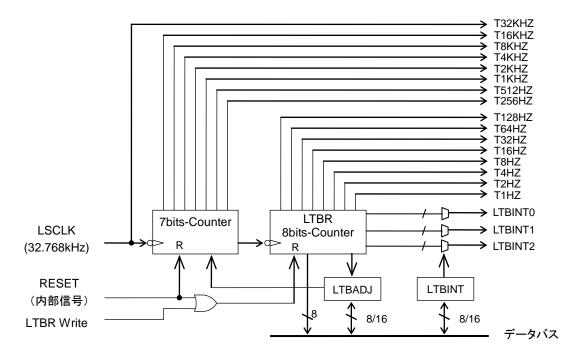

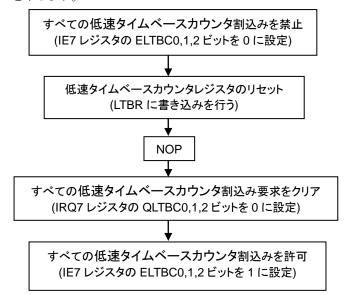

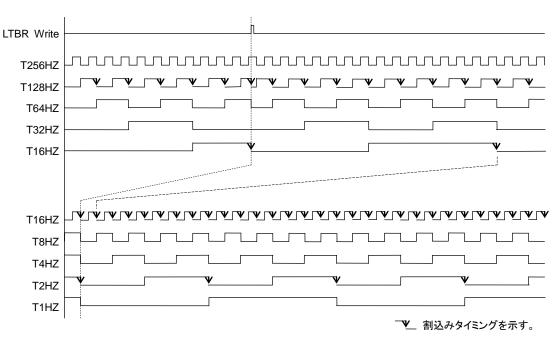

|            |         | 低速タイムベースカウンタ                                                                              |      |

|            |         |                                                                                           |      |

|            |         |                                                                                           |      |

| 第8         | 3 章 タ   | イマ                                                                                        |      |

|            |         |                                                                                           | Q_1  |

|            |         |                                                                                           |      |

| Ü          |         | 特長                                                                                        |      |

|            |         | 構成                                                                                        |      |

| Ω          |         | ·\$D                                                                                      |      |

| O          |         | レジスター覧                                                                                    |      |

|            |         | タイマ nm データレジスタ(TMnmD:{n,m}={0,1} , {2,3} , {4,5} , {6,7})                                 |      |

|            |         | タイマ nm カウンタレジスタ (TMnmC: {n,m}={0,1}, {2,3}, {4,5}, {6,7})                                 |      |

|            |         |                                                                                           |      |

|            |         | タイマ nm コントロールレジスタ(TMnmCON : {n,m}={0,1} , {2,3} , {4,5} , {6,7})<br>タイマスタートレジスタ 0(TMSTR0) |      |

|            |         | ,                                                                                         |      |

|            |         | タイマストップレジスタ 0(TMSTP0)                                                                     |      |

| 0          |         | タイマステータスレジスタ 0(TMSTAT0)                                                                   |      |

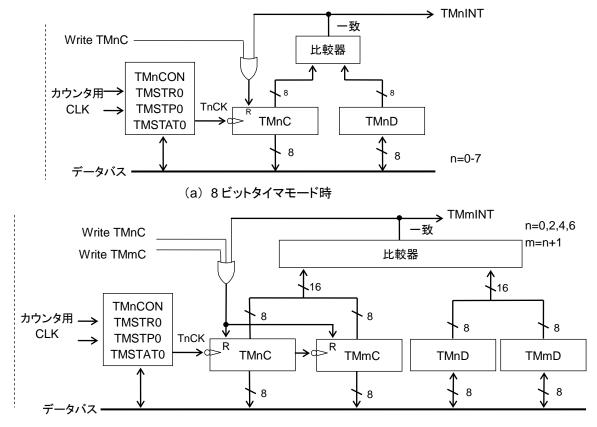

| 8          |         | 说明                                                                                        |      |

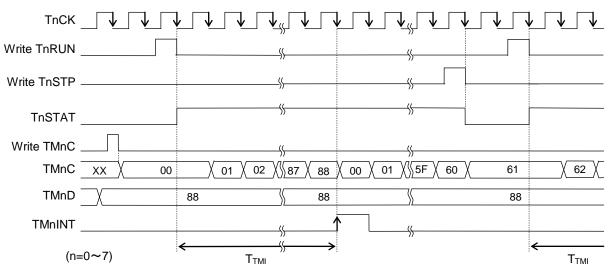

|            |         | 通常タイマモード動作                                                                                |      |

|            |         | ワンショットタイマモード動作                                                                            |      |

|            | 8.3.3   | 16 ビットタイマモード動作                                                                            | 8-12 |

|            |         |                                                                                           |      |

|            |         |                                                                                           |      |

| <u>第 9</u> | 9 章 多   | 機能タイマ(FTM)                                                                                |      |

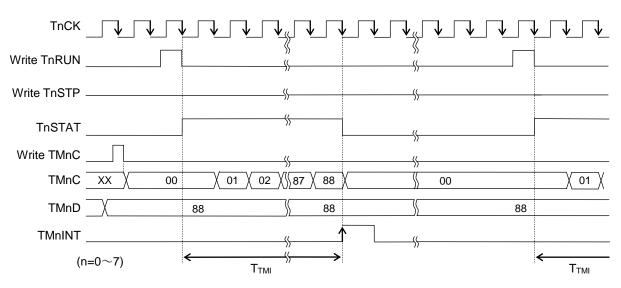

| 0 夕        |         | ₹(FTM)                                                                                    | 0.1  |

|            |         |                                                                                           |      |

| 9          | ).1 概要. | #± E                                                                                      |      |

|            |         | 特長###                                                                                     |      |

|            |         | 構成                                                                                        |      |

| _          |         | 端子一覧                                                                                      |      |

| 9          |         | 夕説明                                                                                       |      |

|            |         | レジスター覧                                                                                    |      |

|            |         | FTMn 周期レジスタ (FTnP: n=0,1,2,3)                                                             |      |

|            |         | FTMn イベントレジスタ A (FTnEA: n=0,1,2,3)                                                        |      |

|            |         | FTMn イベントレジスタ B (FTnEB: n=0,1,2,3)                                                        |      |

|            |         | FTMn デッドタイムレジスタ(FTnDT: n=0,1,2,3)                                                         |      |

|            |         | FTMn カウンタレジスタ(FTnC: n=0,1,2,3)                                                            |      |

|            |         | FTMn コントロールレジスタ 0 (FTnCON0: n=0,1,2,3)                                                    |      |

|            |         | FTMn コントロールレジスタ 1 (FTnCON1: n=0,1,2,3)                                                    |      |

|            |         | FTMn モードレジスタ(FTnMOD: n=0,1,2,3)                                                           |      |

|            |         | ) FTMn クロックレジスタ(FTnCLK: n=0,1,2,3)                                                        |      |

|            |         | FTMn トリガレジスタ 0 (FTnTRG0 : n=0,1,2,3)                                                      |      |

|            |         | 2 FTMn トリガレジスタ 1(FTnTRG1 : n=0,1,2,3)                                                     |      |

|            | 9.2.13  | 3 FTMn 割込みイネーブルレジスタ (FTnINTE: n=0,1,2,3)                                                  | 9-22 |

|            |         | 4 FTMn 割込みステータスレジスタ(FTnINTS:n=0,1,2,3)                                                    |      |

|            | 9.2.1   | 5 FTMn 割込みクリアレジスタ(FTnINTC: n=0,1,2,3)                                                     | 9-26 |

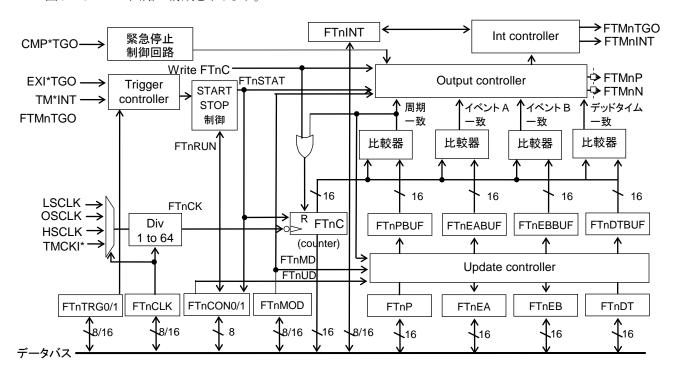

|            | 9.2.10  | 6 FTM 出力 nm 選択レジスタ(FTOnmSL: n = 0,2,4,6,8,A,C,E, m=n+1)                                   | 9-27 |

| 9.3 動作説明                                                | 9-29                 |

|---------------------------------------------------------|----------------------|

| 9.3.1 共通シーケンス                                           | 9-29                 |

| 9.3.2 カウンタ動作                                            | 9-31                 |

| 9.3.2.1 ソフトウェアによるカウント開始/停止                              | 9-31                 |

| 9.3.2.2 トリガイベントによるカウント開始/停止                             |                      |

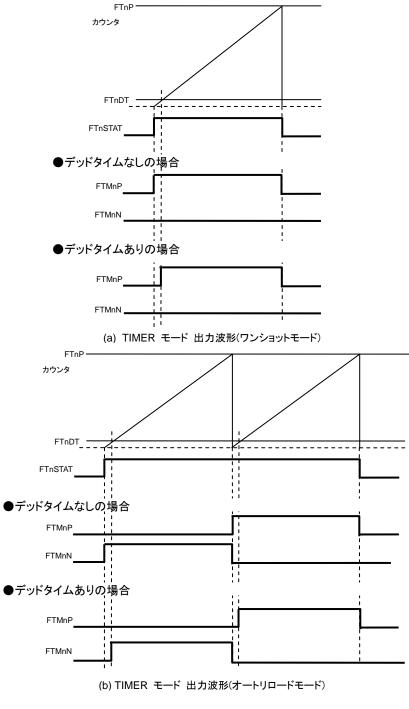

| 9.3.3 TIMER モードの動作                                      | 9-32                 |

| 9.3.3.1 TIMER モードの出力波形                                  | 9-32                 |

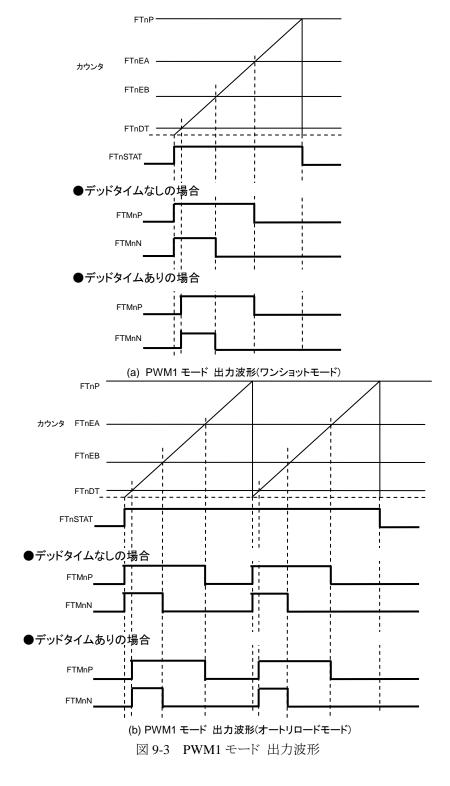

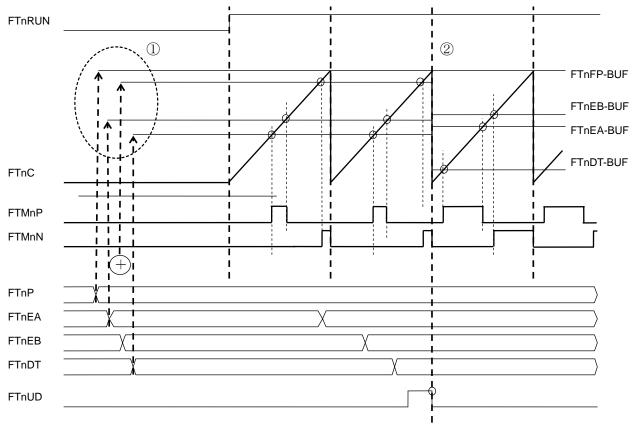

| 9.3.4 PWM1 モードの動作                                       | 9-34                 |

| 9.3.4.1 PWM1 モードの出力波形                                   | 9-34                 |

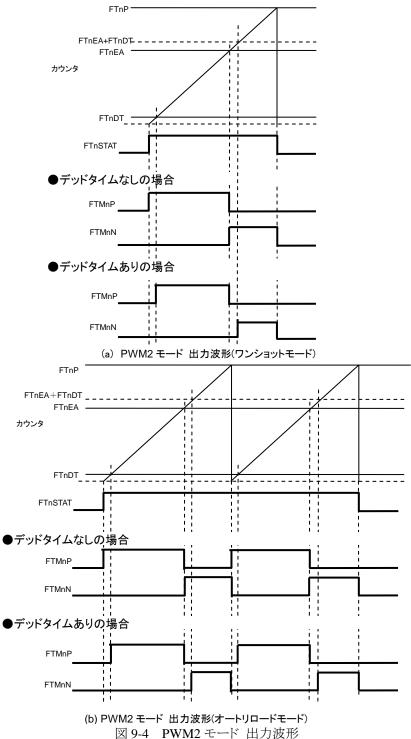

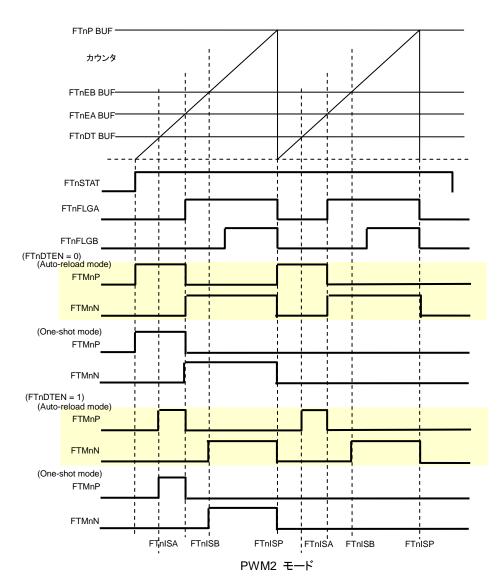

| 9.3.5 PWM2 モードの動作                                       |                      |

| 9.3.5.1 PWM2 モードの出力波形                                   | 9-35                 |

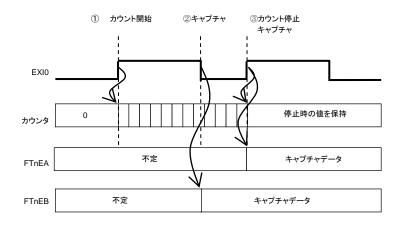

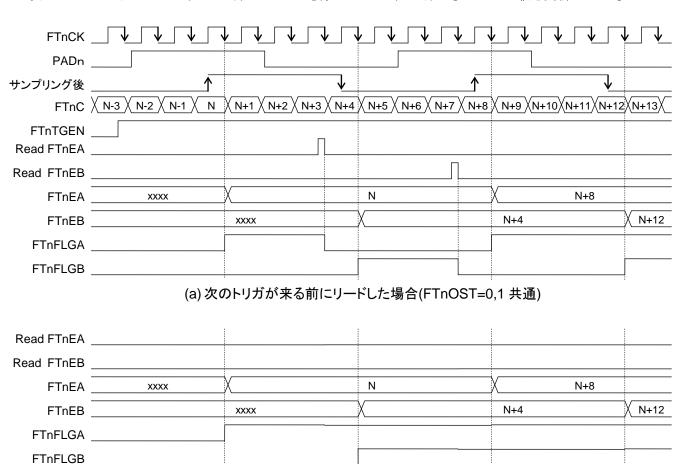

| 9.3.6 CAPTURE モードの動作                                    |                      |

| 9.3.6.1 CAPTURE モードの測定例                                 | 9-37                 |

| 9.3.7 イベント/緊急停止トリガ制御                                    | 9-39                 |

| 9.3.7.1 イベント信号について                                      |                      |

| 9.3.7.2 イベントトリガによるスタート、ストップ動作                           | 9-40                 |

| 9.3.7.3 緊急停止動作                                          | 9-41                 |

| 9.3.8 カウンタストップ時の出力                                      |                      |

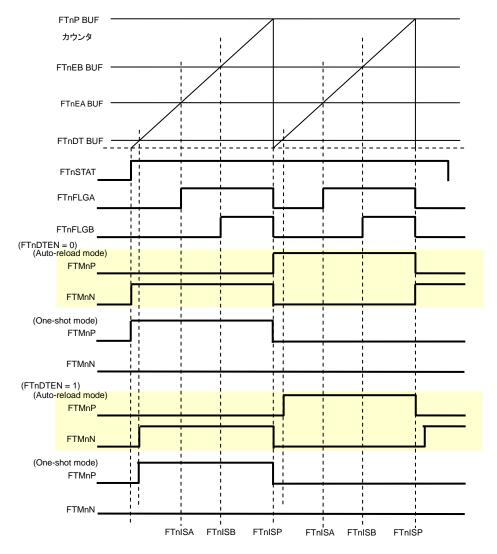

| 9.3.9 周期,イベント A/B,デッドタイムの動作中の変更                         | 9-42                 |

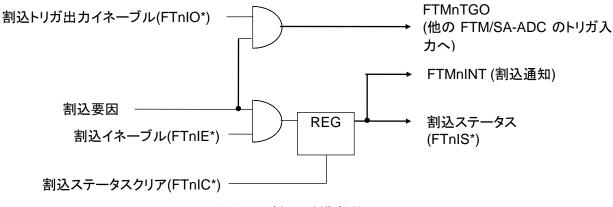

| 9.3.10 割込み要因                                            | 9-43                 |

| 10.1.1 特長                                               | 10-1<br>10-2<br>10-3 |

| 10.2.3 ・フォッテトックダイマモートレンスタ(WDTMOD)                       |                      |

| 10.3.1 ウォッチドッグタイマを使用しない場合の処理例                           |                      |

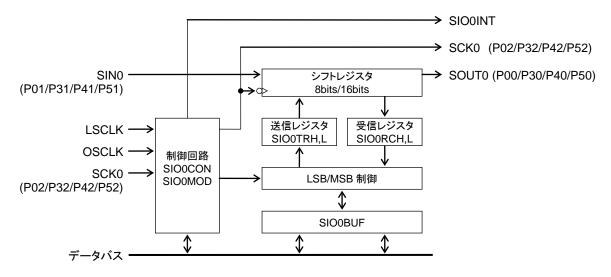

| <u>第 11 章 同期式シリアルポート(SSIO)</u><br>11. 同期式シリアルポート (SSIO) | 11-1                 |

| 11.1 概要                                                 |                      |

| <br>11.1.1 特長                                           |                      |

| 11.1.2 構成                                               |                      |

| 11.1.3 端子一覧                                             |                      |

| 11.2 レジスタ説明                                             | 11-2                 |

| 11.2.1 レジスター覧                                           |                      |

| 11.2.2 シリアルポート 0 送受信バッファ (SIO0BUF)                      |                      |

| 11.2.3 シリアルポート 0 コントロールレジスタ (SIO0CON)                   |                      |

| 11.2.4 シリアルポート 0 モードレジスタ (SIO0MOD)                      |                      |

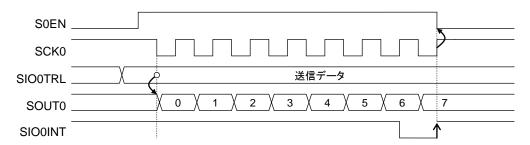

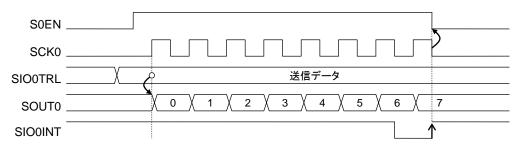

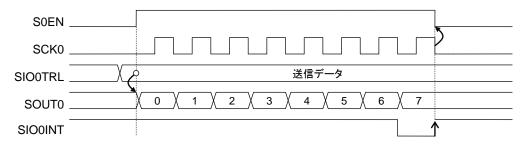

| 11.3 動作説明                                               |                      |

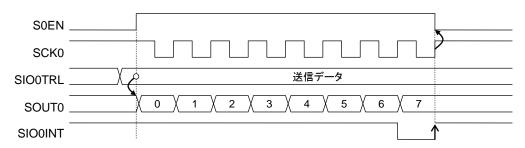

| 11.3.1 送信動作                                             |                      |

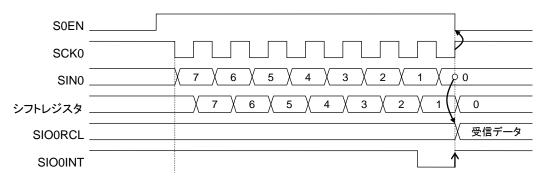

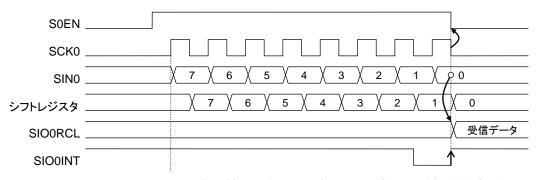

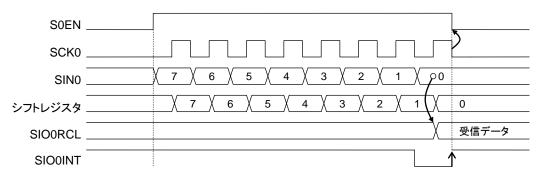

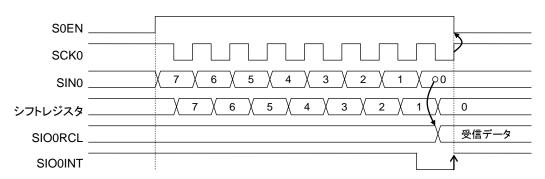

| 11.3.2 受信動作                                             |                      |

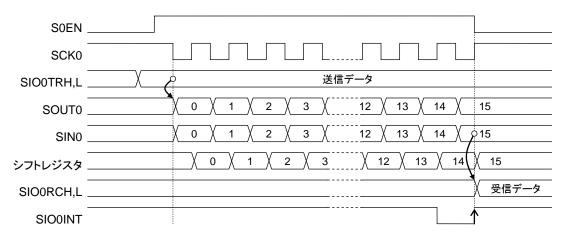

| 11.3.3 送受信動作                                            |                      |

| 11.3.4 端子設定について                                         |                      |

|                                                         |                      |

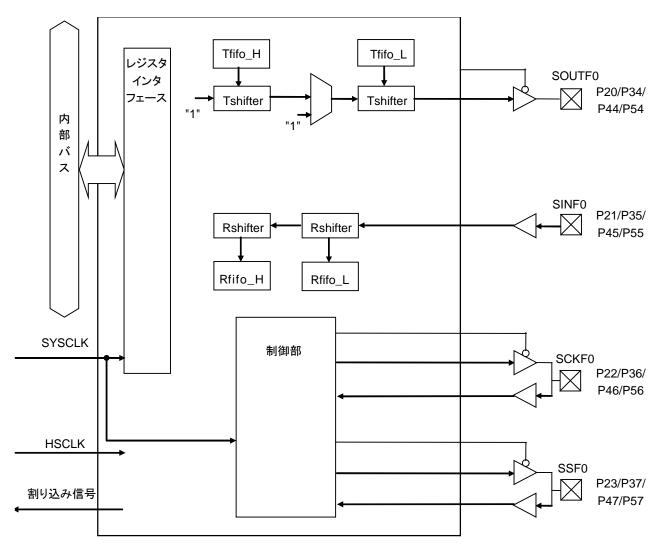

## 第 12 章 FIFO 付同期式シリアルポート(SSIOF)

| 2. FIFO 付同期式シリアルポート(SSIOF)                 | 12-1  |

|--------------------------------------------|-------|

| 12.1 概要                                    | 12-′  |

| 12.1.1 特長                                  | 12-′  |

| 12.1.2 構成                                  | 12-2  |

| 12.1.3 端子一覧                                | 12-2  |

| 12.2 レジスタ説明                                | 12-3  |

| 12.2.1 レジスター覧                              | 12-3  |

| 12.2.2 SIOF0 制御レジスタ (SF0CTRL)              | 12-4  |

| 12.2.3 SIOF0 割込み制御レジスタ (SF0INTC)           | 12-6  |

| 12.2.4 SIOF0 転送間隔制御レジスタ (SF0TRAC)          | 12-8  |

| 12.2.5 SIOF0 ボーレートレジスタ (SF0BRR)            | 12-9  |

| 12.2.6 SIOF0 状態レジスタ (SF0SRR)               |       |

| 12.2.7 SIOF0 状態クリアレジスタ (SF0SRC)            |       |

| 12.2.8 SIOF0FIFO ステータスレジスタ (SF0FSR)        | 12-14 |

| 12.2.9 SIOF0 ライトデータレジスタ (SF0DWR)           | 12-15 |

| 12.2.10 SIOF0 リードデータレジスタ (SF0DRR)          | 12-16 |

| 12.3 動作説明                                  |       |

| 12.3.1 マスタモードとスレーブモード                      | 12-17 |

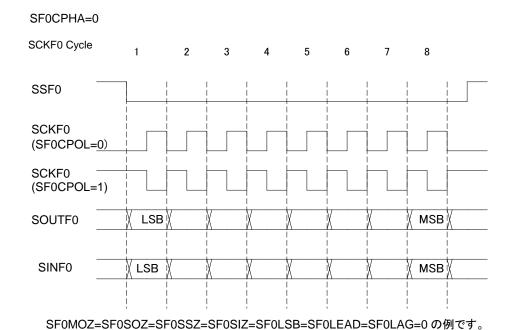

| 12.3.2 シリアルクロックの極性と位相の制御                   |       |

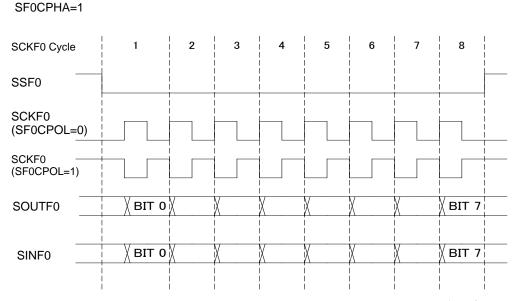

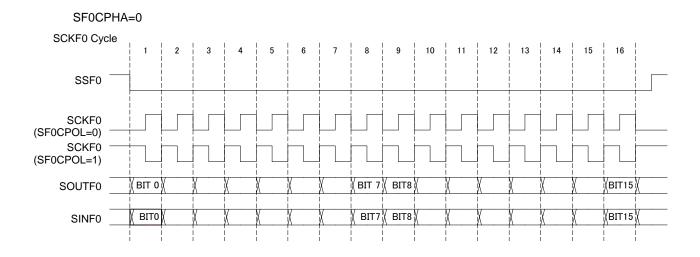

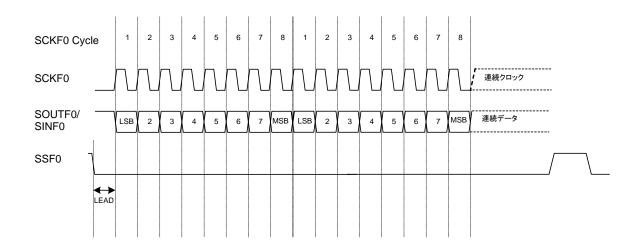

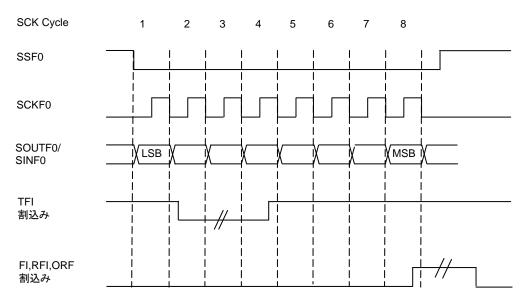

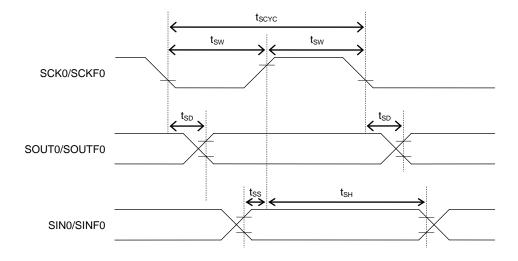

| 12.3.3 SF0CPHA が"0"の場合のデータ転送タイミング          | 12-17 |

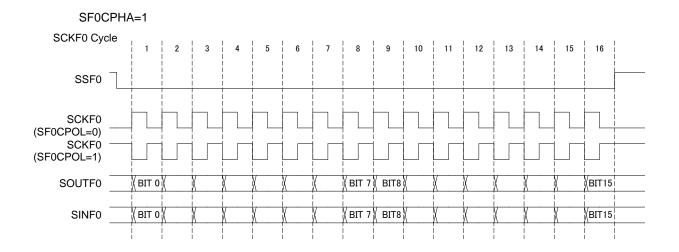

| 12.3.4 SF0CPHA が"1"の場合のデータ転送タイミング          | 12-18 |

| 12.3.5 シリアルクロックボーレート                       | 12-18 |

| 12.3.6 転送サイズ                               | 12-19 |

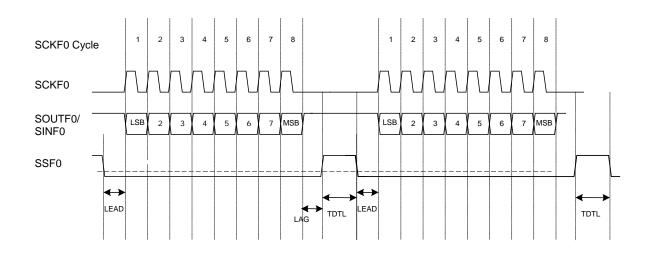

| 12.3.7 転送間隔設定                              | 12-20 |

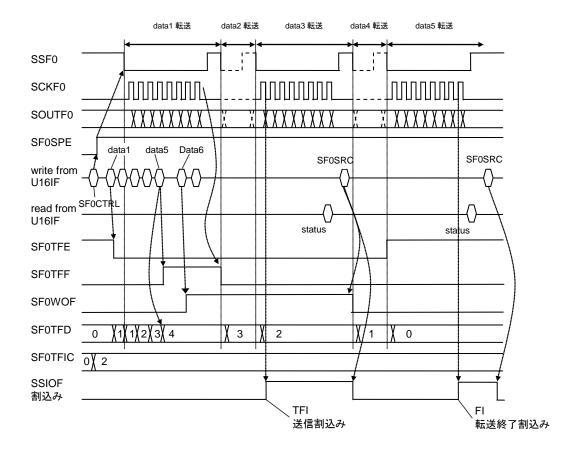

| 12.3.8 送信動作(マスタモード)                        |       |

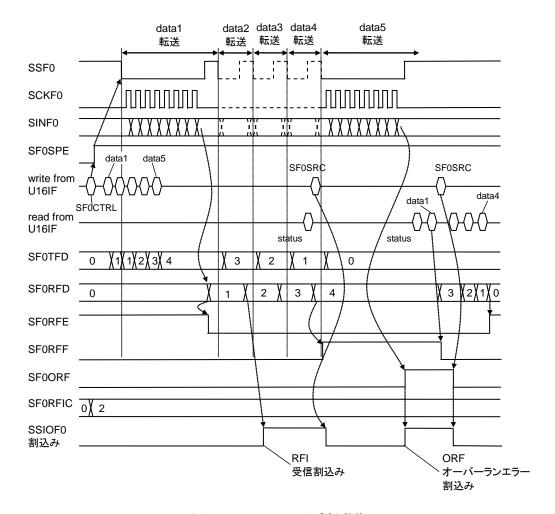

| 12.3.9 受信動作(マスタモード)                        | 12-22 |

| 12.3.10 FIFO 動作                            |       |

| 12.3.11 書き込みオーバフロー                         | 12-23 |

| 12.3.12 オーバーランエラー                          |       |

| 12.3.13 FIFO クリア                           |       |

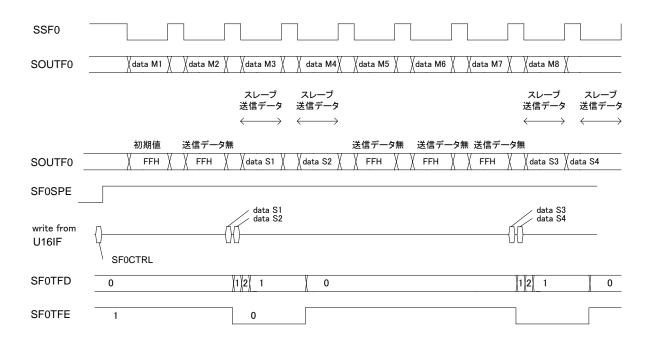

| 12.3.14 スレーブの FIFO 転送 Byte/Word 数が異なる場合の転送 |       |

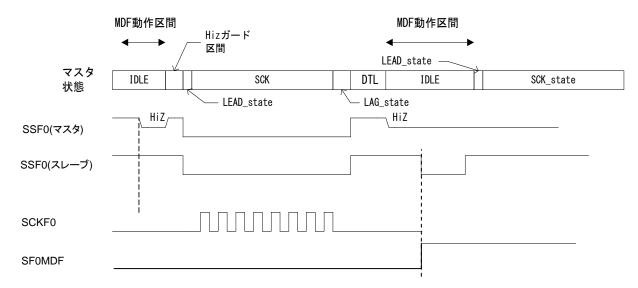

| 12.3.15 モードフォルト(MDF)                       |       |

| 12.3.16 割込み要因                              |       |

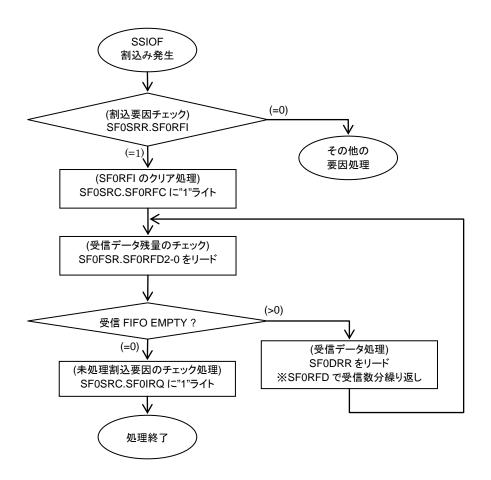

| 12.3.16.1 SSIOF の割込み要因                     |       |

| 12.3.16.2 SSIOF の割込みクリア                    |       |

| 12.3.16.3 SSIOF の割込みタイミング                  |       |

| 12.3.16.4 割込み処理フロー                         |       |

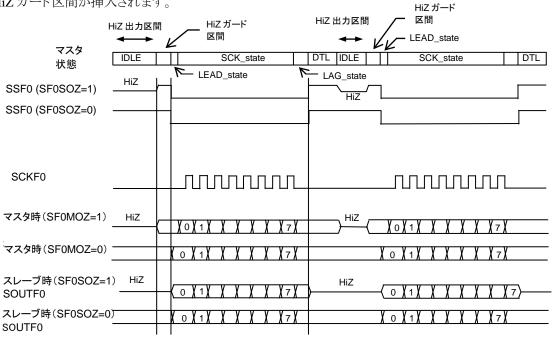

| 12.3.17 Hi-Z の動作                           |       |

| 12.3.18 SF0MST 設定後から転送開始までの時間              |       |

| 12.3.19 端子設定について                           | 12-28 |

|                                            |       |

| 第13章 UART                                  |       |

| 3. UART                                    |       |

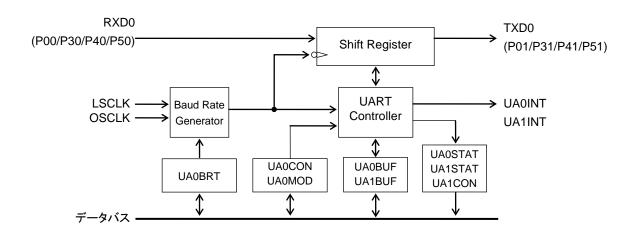

| 13.1 概要                                    |       |

| 13.1.1 特長                                  |       |

| 13.1.2 構成                                  |       |

| 13.1.3 端子一覧                                |       |

| 13.2 レジスタ説明                                |       |

| 13.2.1 レジスター覧                              | 13-2  |

| 13.2.2 UARTO 受信バッファ (UAOBUF)             | 13-3  |

|------------------------------------------|-------|

| 13.2.3 UARTO 送信バッファ (UA1BUF)             |       |

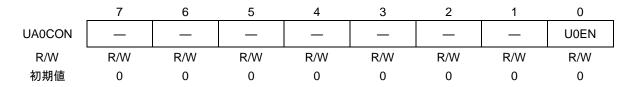

| 13.2.4 UART0 コントロールレジスタ (UA0CON)         |       |

| 13.2.5 UARTO 送信モニタレジスタ (UA1CON)          |       |

| 13.2.6 UARTO モードレジスタ (UA0MOD)            |       |

| 13.2.7 UART0 ボーレートレジスタ (UA0BRT)          |       |

| 13.2.8 UARTO 受信ステータスレジスタ (UAOSTAT)       |       |

| 13.2.9 UARTO 送信ステータスレジスタ (UA1STAT)       |       |

| 13.3 動作説明                                |       |

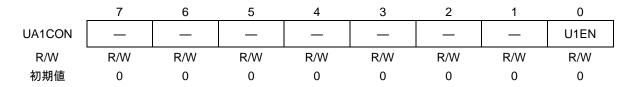

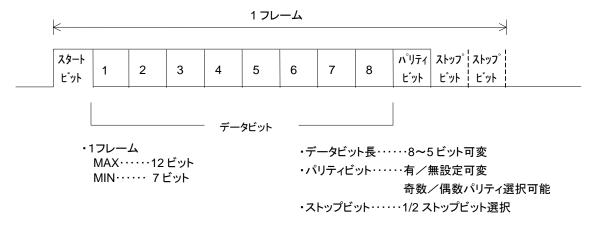

| 13.3.1 転送データフォーマット                       |       |

| 13.3.2 ボーレート                             |       |

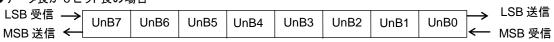

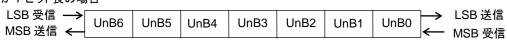

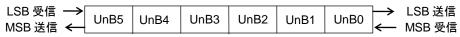

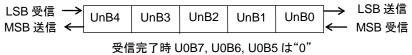

| 13.3.3 送信データ方向                           |       |

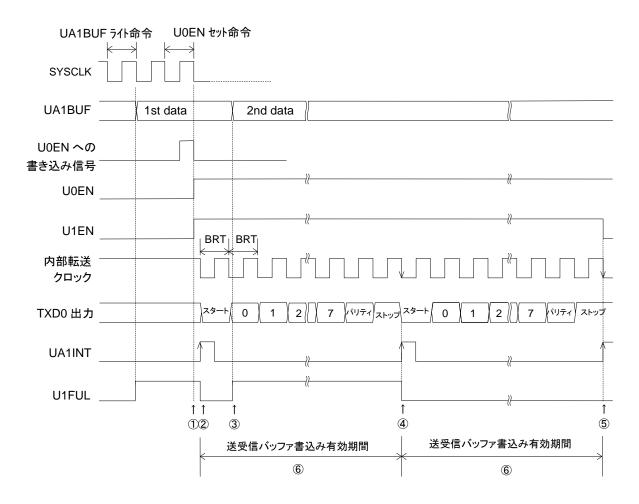

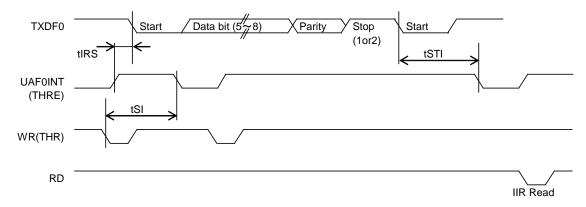

| 13.3.4 送信動作                              |       |

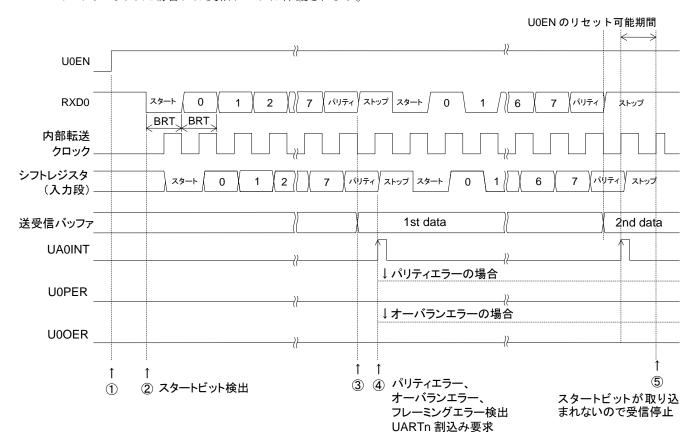

| 13.3.5 受信動作                              |       |

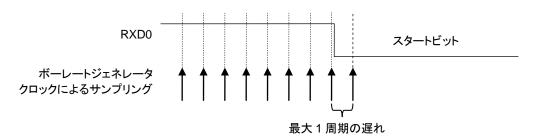

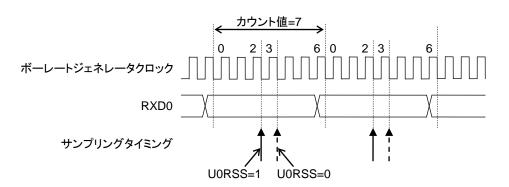

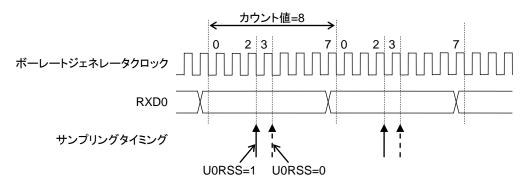

| 13.3.5.1 スタートビットの検出                      |       |

| 13.3.5.2 サンプリングタイミング                     |       |

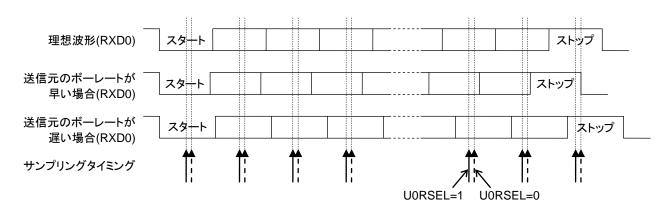

| 13.3.5.3 受信マージン                          |       |

| 10.0.0.0 文旧 (                            | 13-17 |

|                                          |       |

| <u>第 14 章 FIFO 付 UART(UARTF)</u>         |       |

| 14. FIFO 付 UART(UARTF)                   | 14-1  |

| 14.1 概要                                  |       |

| 14.1.1 特長                                |       |

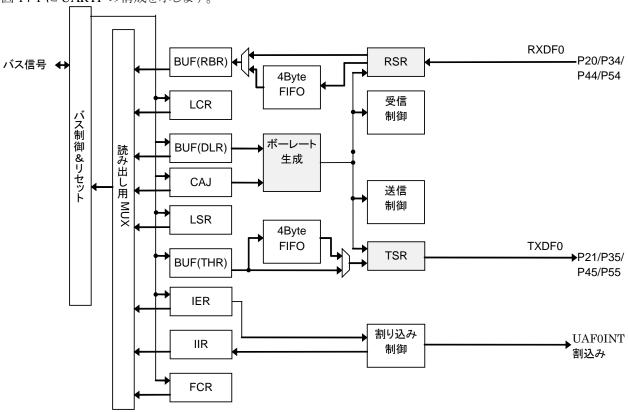

| 14.1.2 構成                                |       |

| 14.1.3 端子一覧                              |       |

| 14.2 レジスタ説明                              |       |

| 14.2.1 レジスター覧                            |       |

| 14.2.2 UARTFO 送受信バッファ (UAFOBUF)          |       |

| 14.2.3 UARTFO 割込みイネーブルレジスタ (UAFOIER)     |       |

| 14.2.4 UARTFO 割込みステータスレジスタ (UAFOIIR)     |       |

| 14.2.5 UARTF0 モードレジスタ (UAF0MOD)          |       |

| 14.2.6 UARTF0 ラインステータスレジスタ (UAF0LSR)     |       |

| 14.2.7 UARTFO クロック調整レジスタ (UAFOCAJ)       |       |

| 14.2.8 UARTFO 割込み要求レジスタ (UAFOIRQ)        |       |

| 14.3 動作説明                                |       |

| 14.3.1 データ送信                             |       |

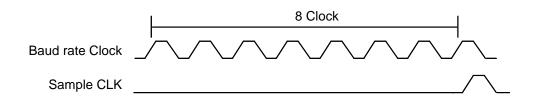

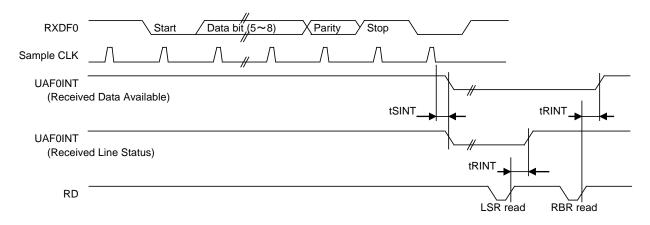

| 14.3.2 データ受信                             |       |

| 14.3.3 ボーレートクロック生成                       |       |

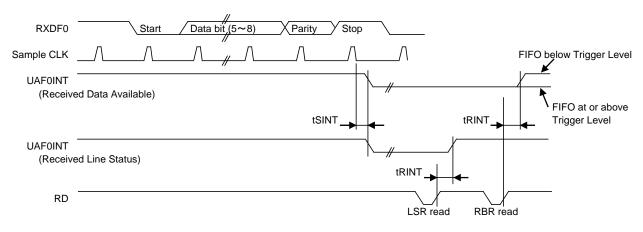

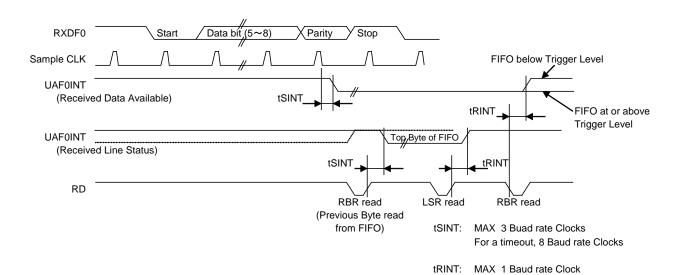

| 14.3.4 FIFO モード                          |       |

| 14.3.5 FIFO ポールモード                       | 14-21 |

| 14.3.6 エラーステータス                          |       |

| 14.3.7 ブロックコントロールによる初期化の注意事項             |       |

|                                          |       |

| 第 15 音 1 <sup>2</sup> ○ バフ <i>ハト</i> ローフ |       |

| 第 15 章 I <sup>2</sup> C バスインタフェース        |       |

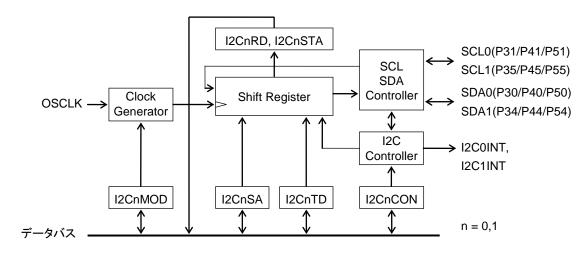

| 15. I <sup>2</sup> C バスインターフェース          | 15-1  |

| 15.1 概要                                  | 15-1  |

| 15.1.1 特長                                | 15-1  |

| 15.1.2 構成                                | 15-1  |

| 15.1.3 端子一覧                              | 15-1  |

| 15.2 レジスタ説明                              | 15-2  |

| 15.2.1 レジスター   「                         | 15-2  |

| 15.2.2 l <sup>2</sup> C バス n 受信データレジスタ (I2CnRD:n=0,1)          | 15-3  |

|----------------------------------------------------------------|-------|

| 15.2.3 I <sup>2</sup> C バス n スレーブアドレスレジスタ (I2CnSA:n=0,1)       | 15-4  |

| 15.2.4 I <sup>2</sup> C バス n 送信データレジスタ (I2CnTD:n=0,1)          | 15-5  |

| 15.2.5 I <sup>2</sup> C バス n コントロールレジスタ (I2CnCON:n=0,1)        | 15-6  |

| 15.2.6 I <sup>2</sup> C バス n モードレジスタ (I2CnMOD:n=0,1)           | 15-8  |

| 15.2.7  I <sup>2</sup> C バス n ステータスレジスタ (I2CnSTA:n=0,1)        | 15-10 |

| 15.3 動作説明                                                      |       |

| 15.3.1 通信動作モード                                                 |       |

| 15.3.1.1 スタートコンディション                                           |       |

| 15.3.1.2 再スタートコンディション                                          |       |

| 15.3.1.3 スレーブアドレス送信モード                                         |       |

| 15.3.1.4 データ送信モード                                              |       |

| 15.3.1.5 データ受信モード                                              |       |

| 15.3.1.6 コントロールレジスタ設定待ち状態                                      | 15-11 |

| 15.3.1.7 ストップコンディション                                           |       |

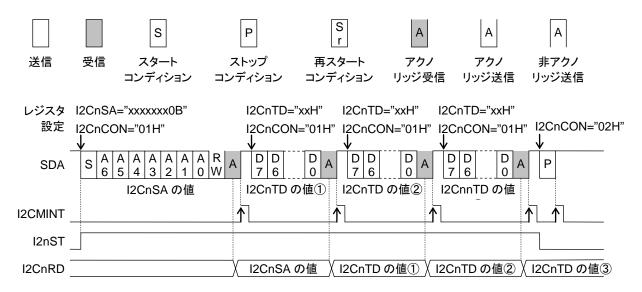

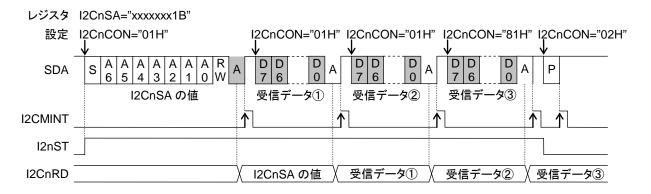

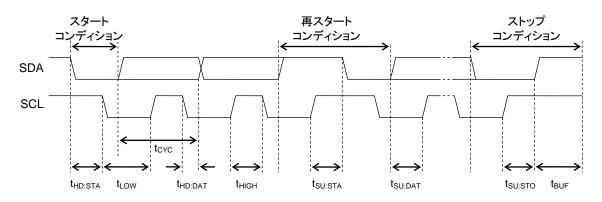

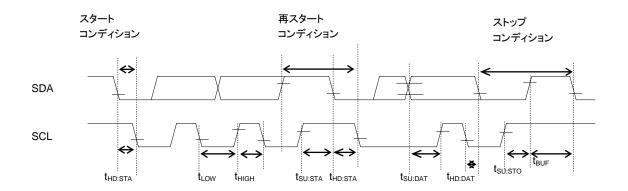

| 15.3.2 通信動作タイミング                                               | 15-13 |

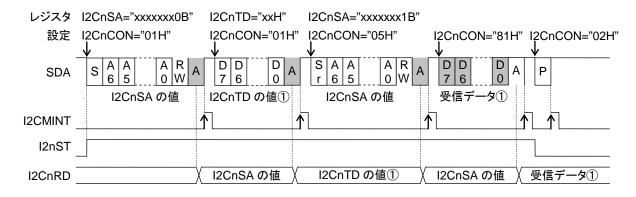

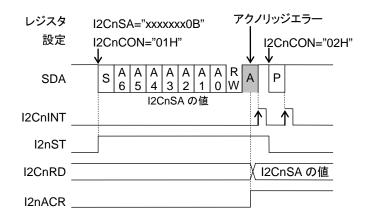

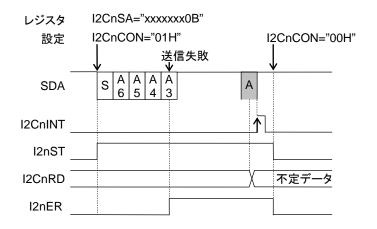

| 15.3.3 動作波形                                                    | 15-15 |

| 15.3.4 端子設定について                                                | 15-16 |

|                                                                |       |

|                                                                |       |

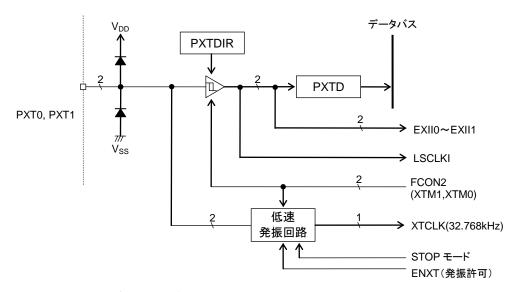

| <u>第 16 章 ポート XT</u>                                           |       |

|                                                                | 40.4  |

| 16. ポート XT                                                     |       |

| 16.1 概要                                                        |       |

| 16.1.1 特長                                                      |       |

| 16.1.2 構成                                                      |       |

| 16.1.3 端子一覧                                                    |       |

| 16.2 レジスタ説明                                                    |       |

|                                                                |       |

| 16.2.2 ポート XT データレジスタ (PXTD)16.2.3 ポート XT ディレクションレジスタ (PXTDIR) |       |

| 16.2.3 ホートストディレッションレッスタ (PATDIR)                               |       |

|                                                                |       |

| 16.3.1 入力ポート機能                                                 | 10-3  |

| 10.3.2 人力小一下以外の 1 次機能                                          | 16-2  |

|                                                                |       |

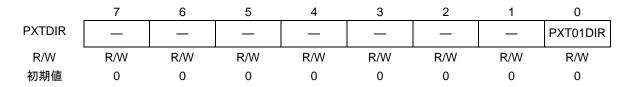

| <u>第 17 章 ポート 0</u>                                            |       |

| 17. ポート 0                                                      | 17-1  |

| 17.1 概要                                                        |       |

| 17.1.1 特長                                                      |       |

| 17.1.2 構成                                                      |       |

| 17.1.3 端子一覧                                                    |       |

| 17.2 レジスタ説明                                                    |       |

| 17.2.1 レジスター覧                                                  |       |

| 17.2.2 ポート 0 データレジスタ (POD)                                     |       |

| 17.2.3 ポート 0 ディレクションレジスタ (P0DIR)                               |       |

| 17.2.4 ポート 0 コントロールレジスタ (POCON)                                |       |

| 17.2.5 ポート 0 モードレジスタ (P0MOD)                                   |       |

| 17.3 動作説明                                                      |       |

| 17.3.1 入出力ポート機能                                                |       |

| 17.3.2 入出力ポート以外の 1 次機能                                         |       |

| 17.3.3 2 次機能~4 次機能                                             |       |

|                                                                |       |

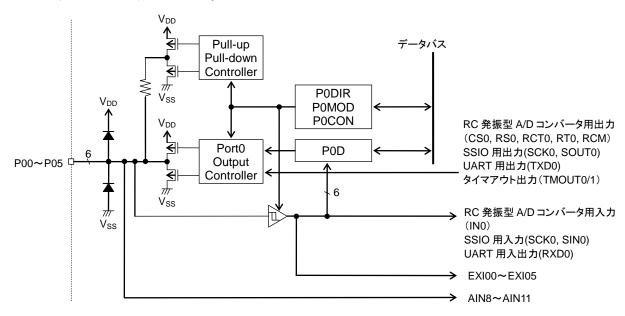

## 第 18 章 ポート 1

| 18.     | ポート1                             | 18-1  |

|---------|----------------------------------|-------|

|         | 18.1 概要                          |       |

|         | 18.1.1 特長                        |       |

|         | 18.1.2 構成                        | 18-1  |

|         | 18.1.3 端子一覧                      |       |

|         | 18.2 レジスタ説明                      |       |

|         | 18.2.1 レジスター覧                    |       |

|         | 18.2.2 ポート 1 データレジスタ (P1D)       |       |

|         | 18.2.3 ポート 1 ディレクションレジスタ (P1DIR) |       |

|         | 18.2.4 ポート 1 コントロールレジスタ (P1CON)  |       |

|         | 18.3 動作説明                        |       |

|         | 18.3.1 入出力ポート機能                  |       |

|         | 18.3.2 入出力ポート以外の 1 次機能           |       |

|         |                                  |       |

| 华       | 40 辛 ピーレン                        |       |

| <u></u> | 19章 ポート2                         |       |

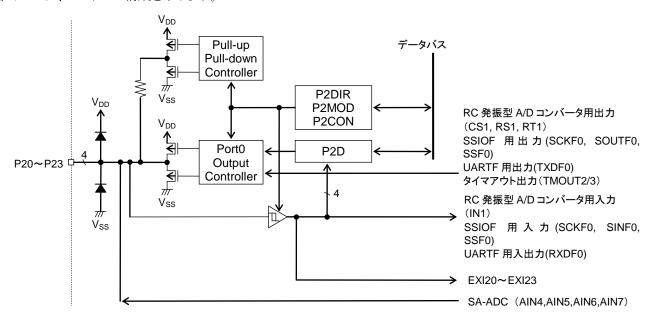

| 19.     | ポート 2                            |       |

|         | 19.1 概要                          | 19-1  |

|         | 19.1.1 特長                        | 19-1  |

|         | 19.1.2 構成                        | 19-2  |

|         | 19.1.3 端子一覧                      | 19-3  |

|         | 19.2 レジスタ説明                      | 19-4  |

|         | 19.2.1 レジスター覧                    | 19-4  |

|         | 19.2.2 ポート 2 データレジスタ (P2D)       | 19-5  |

|         | 19.2.3 ポート 2 ディレクションレジスタ (P2DIR) | 19-6  |

|         | 19.2.4 ポート 2 コントロールレジスタ (P2CON)  |       |

|         | 19.2.5 ポート 2 モードレジスタ (P2MOD)     |       |

|         | 19.3 動作説明                        | 19-10 |

|         | 19.3.1 入出力ポート機能                  | 19-10 |

|         | 19.3.2 入出力ポート以外の 1 次機能           | 19-10 |

|         | 19.3.3 2次機能~4次機能                 | 19-10 |

|         |                                  |       |

| 笙       | 20 章 ポート3                        |       |

|         |                                  |       |

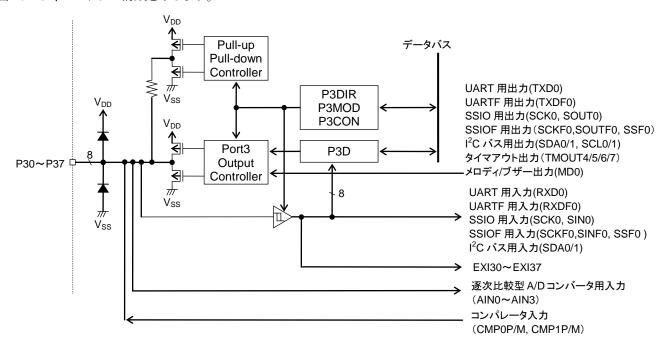

| 20.     | ポート 3                            |       |

|         | 20.1 概要                          |       |

|         | 20.1.1 特長                        |       |

|         | 20.1.2 構成                        |       |

|         | 20.1.3 端子一覧                      |       |

|         | 20.2 レジスタ説明                      |       |

|         | 20.2.1 レジスター覧                    |       |

|         | 20.2.2 ポート 3 データレジスタ (P3D)       |       |

|         | 20.2.3 ポート 3 ディレクションレジスタ (P3DIR) |       |

|         | 20.2.4 ポート 3 コントロールレジスタ (P3CON)  |       |

|         | 20.2.5 ポート 3 モードレジスタ (P3MOD)     |       |

|         | 20.3 動作説明                        |       |

|         | 20.3.1 入出力ポート機能                  |       |

|         | 20.3.2 入出力ポート以外の 1 次機能           |       |

|         | 20.3.3 2次機能~4次機能                 | 20-12 |

## 第 21 章 ポート 4

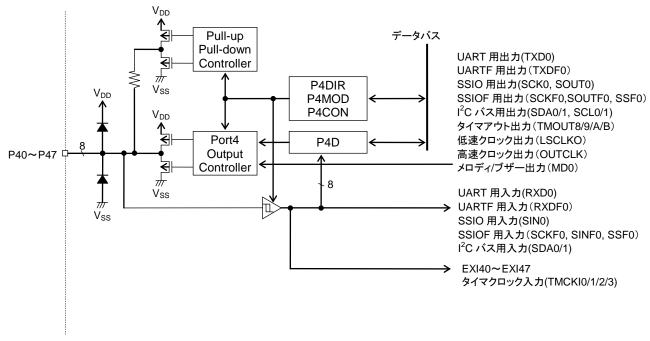

| 21. ポート 4                          | 21-1  |

|------------------------------------|-------|

| 21.1 概要                            |       |

| 21.1.1 特長                          | 21-1  |

| 21.1.2 構成                          | 21-2  |

| 21.1.3 端子一覧                        | 21-3  |

| 21.2 レジスタ説明                        |       |

| 21.2.1 レジスター覧                      | 21-4  |

| 21.2.2 ポート 4 データレジスタ (P4D)         | 21-5  |

| 21.2.3 ポート 4 ディレクションレジスタ (P4DIR)   | 21-6  |

| 21.2.4 ポート4コントロールレジスタ (P4CON)      | 21-7  |

| 21.2.5 ポート 4 モードレジスタ (P4MOD)       | 21-9  |

| 21.3 動作説明                          | 21-11 |

| 21.3.1 入出力ポート機能                    |       |

| 21.3.2 入出力ポート以外の 1 次機能             |       |

| 21.3.3 2 次機能~4 次機能                 | 21-1′ |

|                                    |       |

|                                    |       |

| 第 22 章 ポート 5                       |       |

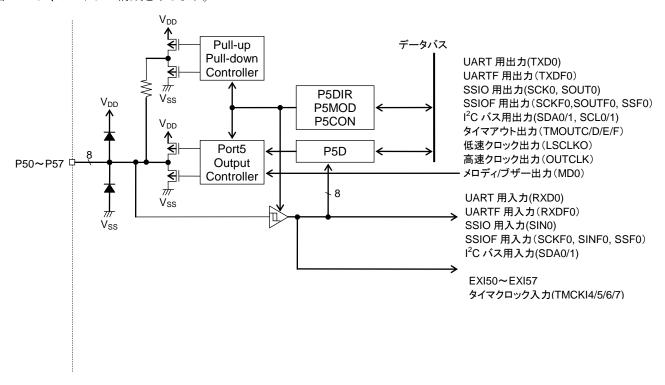

| 22. ポート 5                          | 22-1  |

| 22.1 概要                            |       |

| 22.1.1 特長                          |       |

| 22.1.2 構成                          |       |

| 22.1.3 端子一覧                        |       |

| 22.2 レジスタ説明                        | 22-4  |

| 22.2.1 レジスター覧                      | 22-4  |

| 22.2.2 ポート 5 データレジスタ (P5D)         | 22-5  |

| 22.2.3 ポート 5 ディレクションレジスタ (P5DIR)   | 22-6  |

| 22.2.4 ポート 5 コントロールレジスタ (P5CON)    | 22-7  |

| 22.2.5 ポート 5 モードレジスタ (P5MOD)       | 22-9  |

| 22.3 動作説明                          | 22-11 |

| 22.3.1 入出力ポート機能                    |       |

| 22.3.2 入出力ポート以外の 1 次機能             | 22-11 |

| 22.3.3 2 次機能~4 次機能                 | 22-1′ |

|                                    |       |

|                                    |       |

| 第 23 章 メロディドライバ                    |       |

| 23. メロディドライバ                       | 23-^  |

| 23.1 概要                            | 23-^  |

| 23.1.1 特長                          | 23-1  |

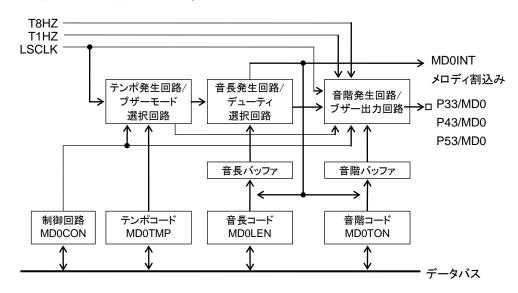

| 23.1.2 構成                          | 23-1  |

| 23.1.3 端子一覧                        | 23-1  |

| 23.2 レジスタ説明                        |       |

| 23.2.1 レジスター覧                      |       |

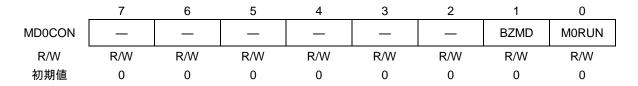

| 23.2.2 メロディ 0 コントロールレジスタ (MD0CON)  |       |

| 23.2.3 メロディ 0 テンポコードレジスタ (MD0TMP)  |       |

| 23.2.3 メロディ 0 音階、音長コードレジスタ (MD0TL) |       |

| 23.3 動作説明                          |       |

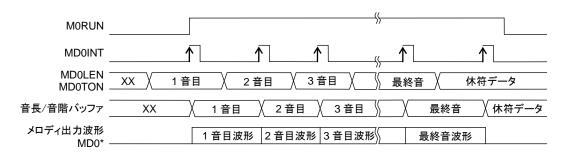

| 23.3.1 メロディ出力の動作                   | 23-7  |

|    | 23.3.2 | メロディ回路の使用例                          | 23-8  |

|----|--------|-------------------------------------|-------|

|    | 23.3.3 | テンポコード                              | 23-9  |

|    | 23.3.4 | 音長コード                               | 23-10 |

|    | 23.3.5 | 音階コード                               | 23-11 |

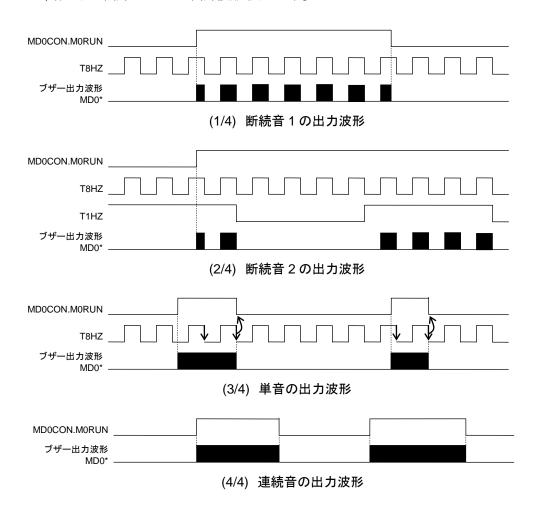

|    |        | ブザー出力の動作                            |       |

|    |        |                                     |       |

| 笙: | 24 章 R | C 発振型 A/D コンバータ(RC-ADC)             |       |

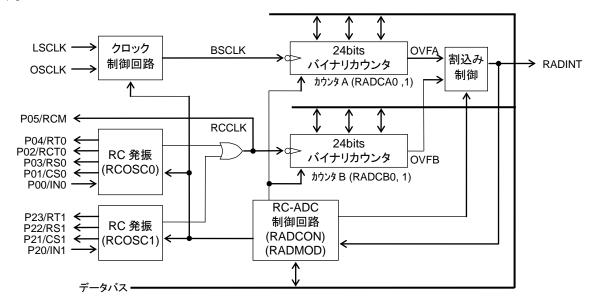

|    |        | A/D コンバータ (RC-ADC)                  | 24-1  |

|    |        | 775 - 27. 7. (10.7150)              |       |

| -  |        | 特長                                  |       |

|    |        | 構成                                  |       |

|    |        | 端子一覧                                |       |

| 2  |        | 、<br>スタ説明                           |       |

|    |        | レジスター覧                              |       |

|    |        | RC-ADC カウンタ A レジスタ 0 (RADCA0)       |       |

|    |        | RC-ADC カウンタ A レジスタ 1(RADCA1)        |       |

|    |        | RC-ADC カウンタ B レジスタ 0 (RADCB0)       |       |

|    |        | RC-ADC カウンタ B レジスタ 1(RADCB1)        |       |

|    |        | RC-ADC モードレジスタ (RADMOD)             |       |

|    |        | RC-ADC コントロールレジスタ (RADCON)          |       |

| 2  |        |                                     |       |

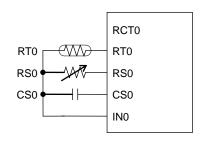

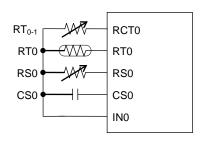

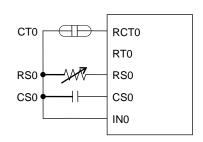

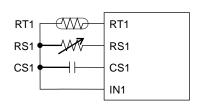

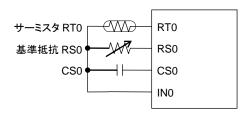

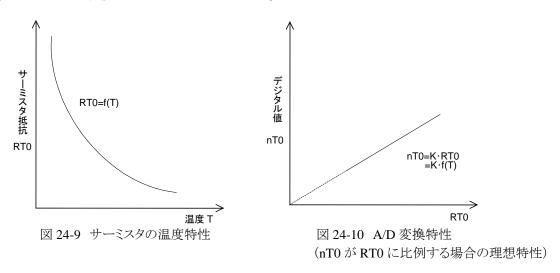

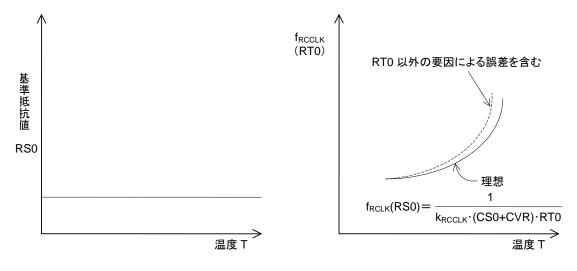

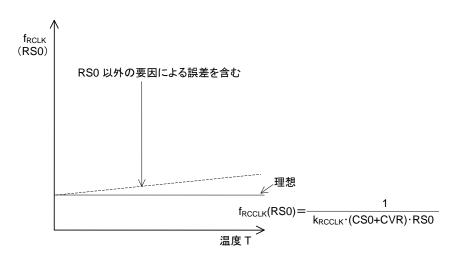

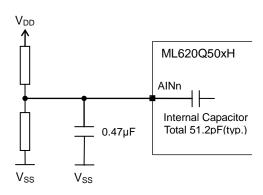

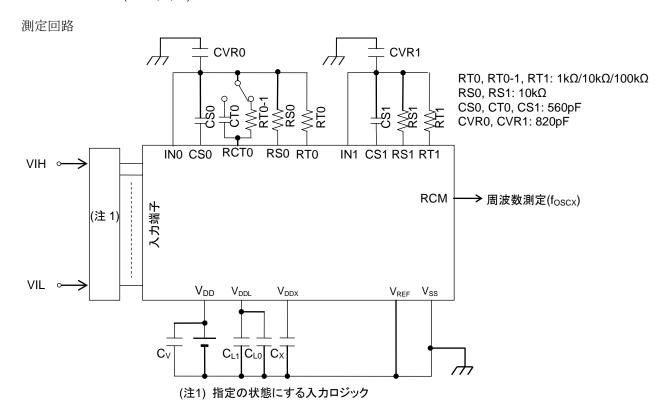

|    | 24.3.1 | RC 発振回路                             | 24-10 |

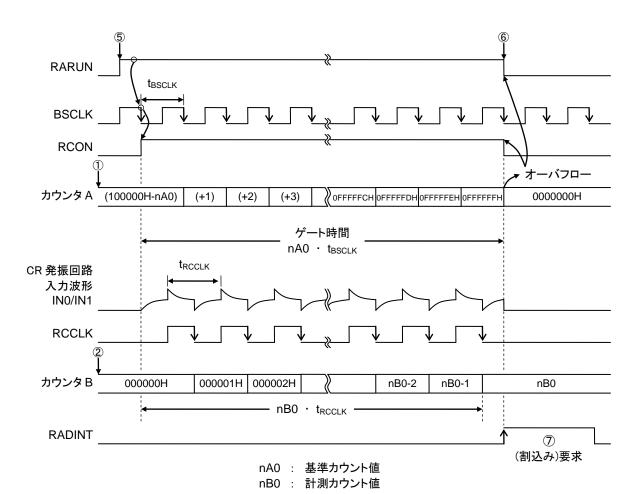

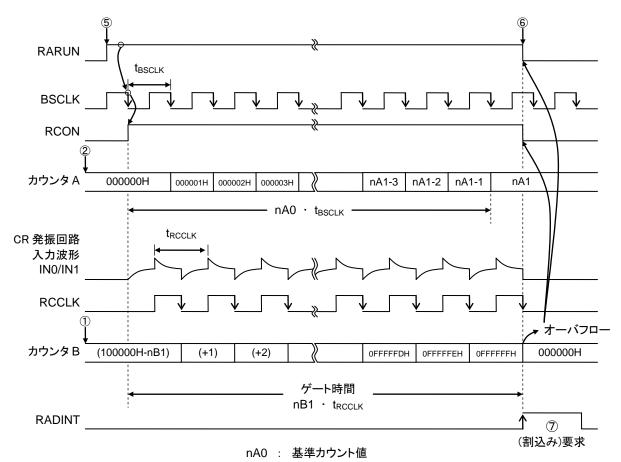

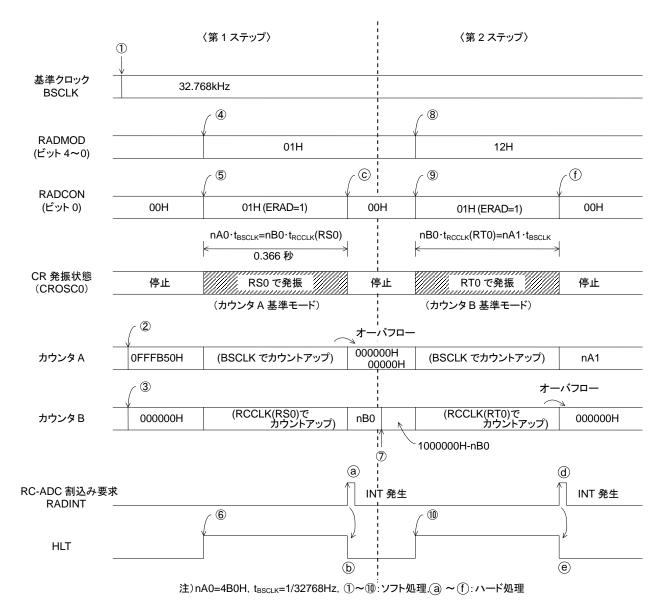

|    | 24.3.2 | カウンタ A/B 基準モード                      | 24-12 |

|    |        | RC 発振型 A/D コンバータの使用例                |       |

|    | 24.3.4 | RC 発振モニタ                            | 24-19 |

|    |        |                                     |       |

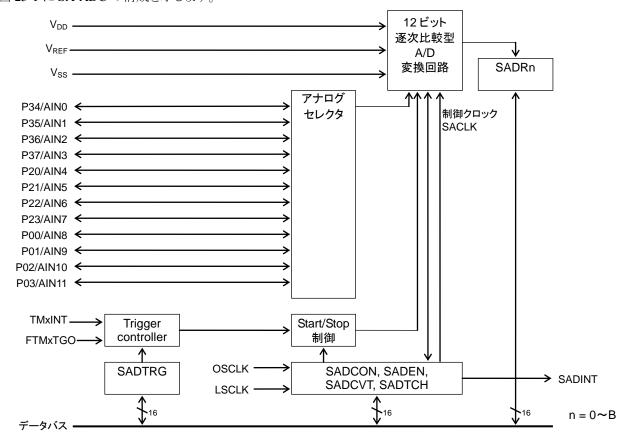

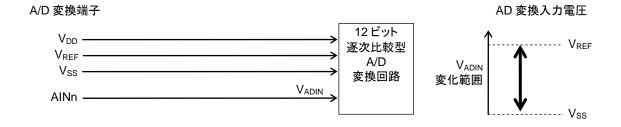

| 第2 | 25 章 逐 | 医次比較型 A/D コンバータ(SA-ADC)             |       |

|    |        |                                     | 25-1  |

|    |        |                                     |       |

| -  |        | 特長                                  |       |

|    |        | 構成                                  |       |

|    |        | 端子一覧                                |       |

| 4  |        | 、<br>スタ説明                           |       |

| -  |        | レジスター覧                              |       |

|    |        | SA-ADC リザルトレジスタ n (SADRn) n=0~9、A、B |       |

|    |        | SA-ADC コントロールレジスタ 0 (SADCON0)       |       |

|    |        | SA-ADC コントロールレジスタ 1 (SADCON1)       |       |

|    |        | SA-ADC イネーブルレジスタ (SADEN)            |       |

|    |        | SA-ADC タッチセンサレジスタ (SADTCH)          |       |

|    |        | SA-ADCトリガレジスタ (SADTRG)              |       |

|    |        | SA-ADC 精度コントロールレジスタ (SADCVT)        |       |

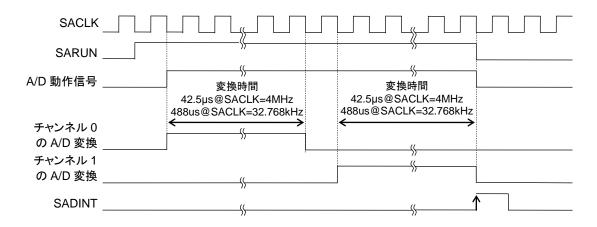

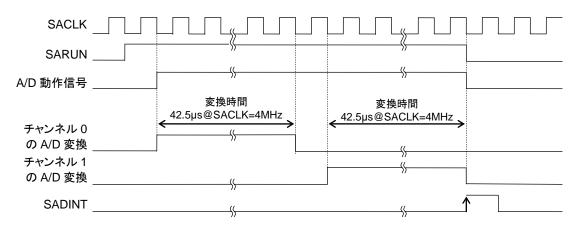

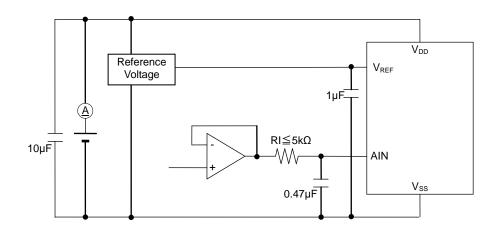

| 2  |        | 説明                                  |       |

|    |        | <br>A/D 変換チャンネルの設定                  |       |

|    |        | 逐次比較型 A/D コンバータの動作                  |       |

|    |        | 静電容量タッチセンス機能動作                      |       |

|    |        | SA-ADC 使用時の注意事項                     |       |

|    |        |                                     |       |

| 笙   | 26 | 音 | アー | $+\Box$      | ブコ  | 11 | ١L | ータ |

|-----|----|---|----|--------------|-----|----|----|----|

| 777 | 20 | = | ,  | <i>,</i> – . | / — | ノィ | ヽレ |    |

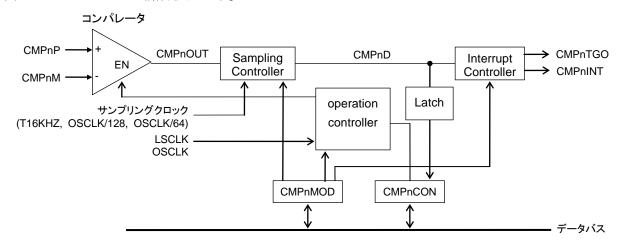

| 26. アナログコンパレータ                             | 26-1 |

|--------------------------------------------|------|

| 26.1 概要                                    |      |

| 26.1.1 特長                                  |      |

| 26.1.2 構成                                  | 26-1 |

| 26.1.3 端子一覧                                | 26-1 |

| 26.2 レジスタ説明                                | 26-2 |

| 26.2.1 レジスター覧                              | 26-2 |

| 26.2.2 コンパレータ n コントロールレジスタ (CMPnCON:n=0,1) | 26-3 |

| 26.2.3 コンパレータ n モードレジスタ (CMPnMOD:n=0,1)    | 26-4 |

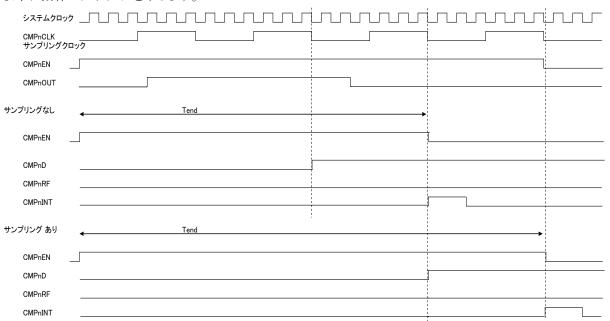

| 26.3 動作説明                                  | 26-6 |

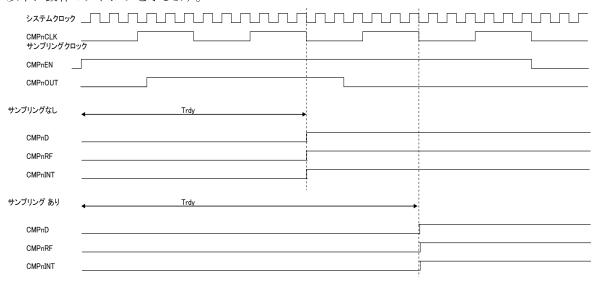

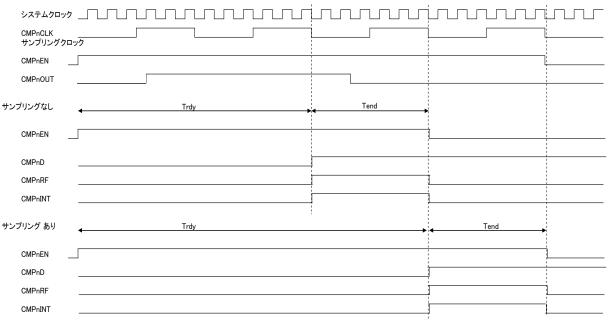

| 26.3.1 コンパレータ機能                            |      |

| 26.3.2 スーパーバイザモード                          | 26-6 |

| 26.3.3 シングルモード                             |      |

| 26.3.4 シングルモニタモード                          | 26-9 |

| 第 27 章 フラッシュメモリ制御                          |      |

|                                            | 27.1 |

| 27. フラッシュァモリ制御                             |      |

| 27.1 似安                                    |      |

| 27.2 レジスタ説明                                |      |

| 27.2.1 レジスター覧                              |      |

| 27.2.2 フラッシュアドレスレジスタ (FLASHA)              |      |

| 27.2.3 フラッシュデータレジスタ (FLASHD)               |      |

| 27.2.4 フラッシュコントロールレジスタ (FLASHCON)          |      |

| 27.2.5 フラッシュアクセプタ (FLASHACP)               |      |

| 27.2.6 フラッシュセグメントレジスタ (FLASHSEG)           |      |

| 27.2.7 フラッシュセルフレジスタ (FLASHSLF)             |      |

| 27.2.8 リマップアドレスレジスタ (REMAPADD)             |      |

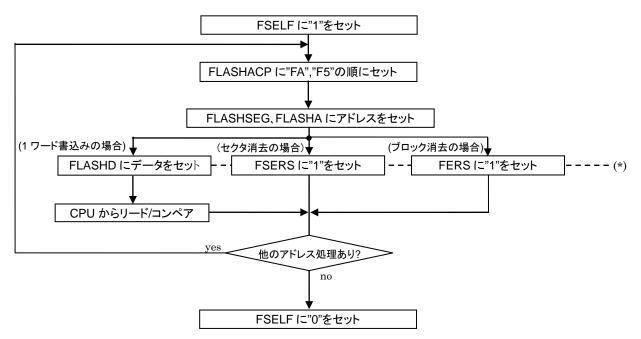

| 27.3 動作説明                                  |      |

| 27.3.1 消去時のアドレス設定                          |      |

|                                            |      |

| 27.3.3 プログラムメモリの書換え(ISP 機能)                |      |

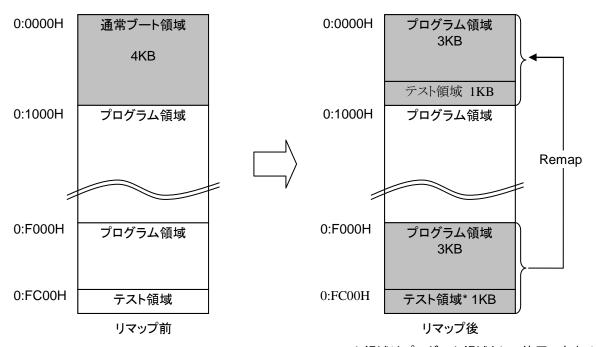

| 27.3.4 ソフトウェアによるブート領域リマップ機能機能              |      |

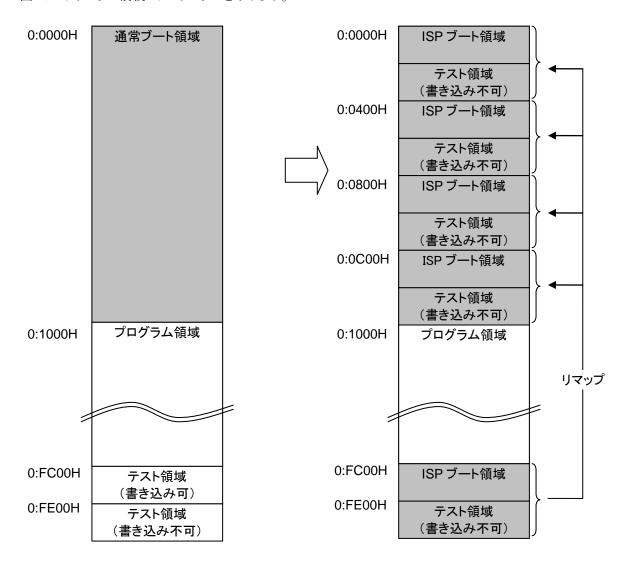

| 27.3.5 ハードウェアによるリマップ機能                     |      |

| 27.3.6 リマップ後のプログラムの注意事項                    |      |

| 27.3.7 プログラム例                              |      |

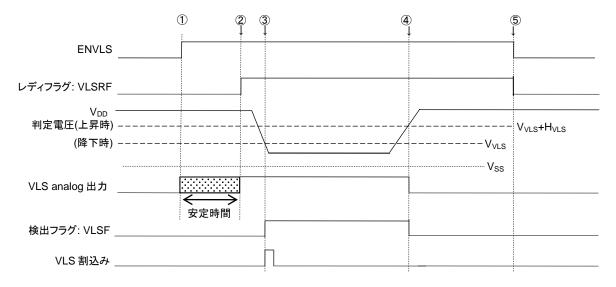

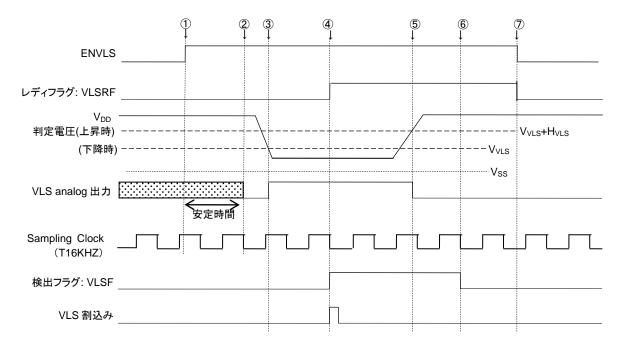

| 第 28 章 電圧レベル検出回路(VLS)                      |      |

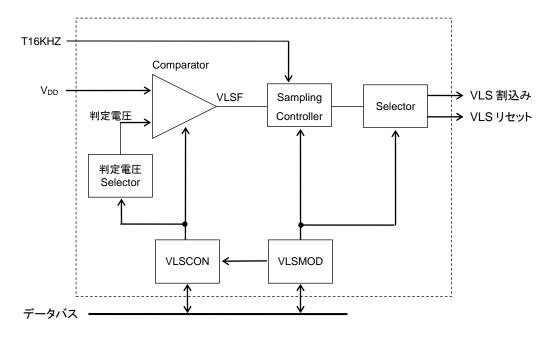

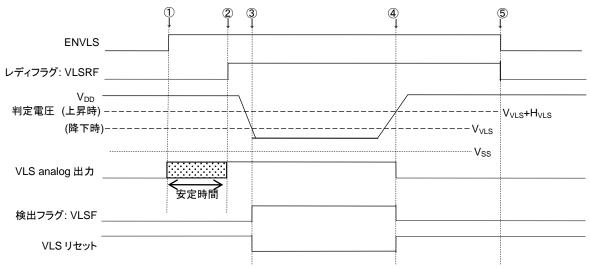

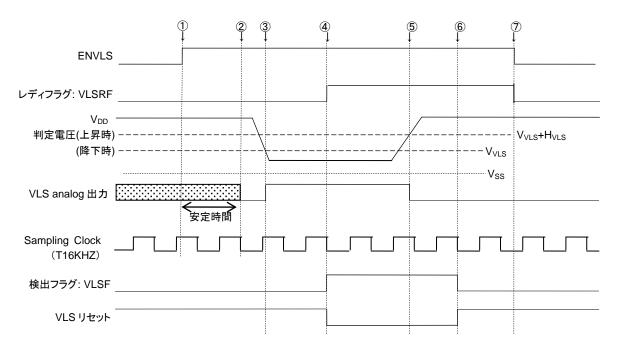

| 28. 電圧レベル検出回路(VLS)                         | 28-1 |

| 28.1 概要                                    |      |

| 28.1.1 特長                                  |      |

| 28.1.2 構成                                  |      |

|                                            |      |

| 28.2.1 レジスター覧                              |      |

| 28.2.2 電圧レベル検出回路コントロールレジスタ (VLSCON)        |      |

| 28.2.3 電圧レベル検出回路モードレジスタ (VLSMOD)           |      |

| 28.3 動作説明                                  | 28-7 |

|                                            |      |

| 28.3.1 スーパーバイザモード                                                                                                         | 28-7 |

|---------------------------------------------------------------------------------------------------------------------------|------|

| <u>第 29 章 LLD 回路</u>                                                                                                      |      |

| 29. LLD 回路                                                                                                                | 29-1 |

| 29.1 概要                                                                                                                   |      |

| 29.1.1 特長                                                                                                                 | 29-1 |

| 29.2 レジスタ説明                                                                                                               |      |

| 29.3 動作説明                                                                                                                 |      |

| 29.3.1 LLD 回路の動作                                                                                                          | 29-1 |

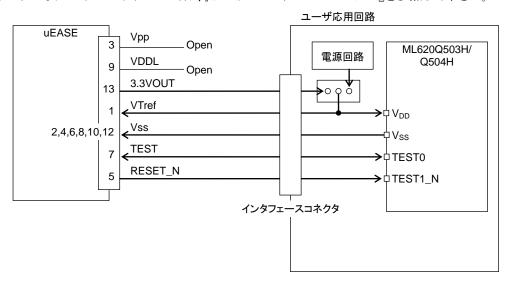

| 第 30 章 オンチップデバッグ機能         30. オンチップデバッグ機能         30.1 概要         30.2 オンチップデバッグエミュレータとの接続方法         30.3 フラッシュメモリ書き換え機能 | 30-1 |

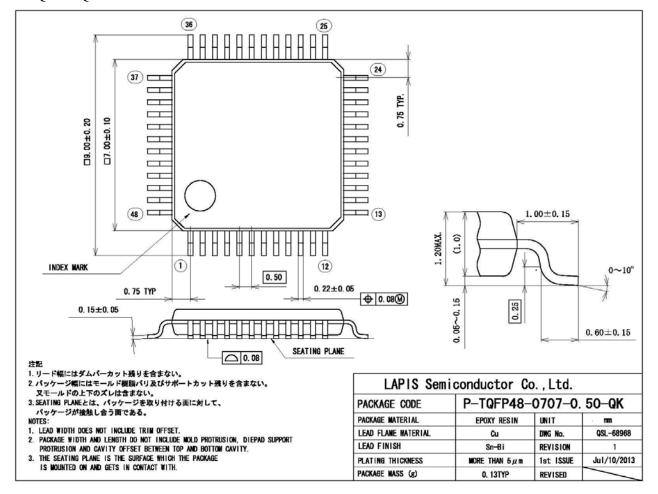

| <u>付録</u><br>付録 A レジスター覧付録 B パッケージ外形図                                                                                     |      |

| 付録 C 電気的特性                                                                                                                |      |

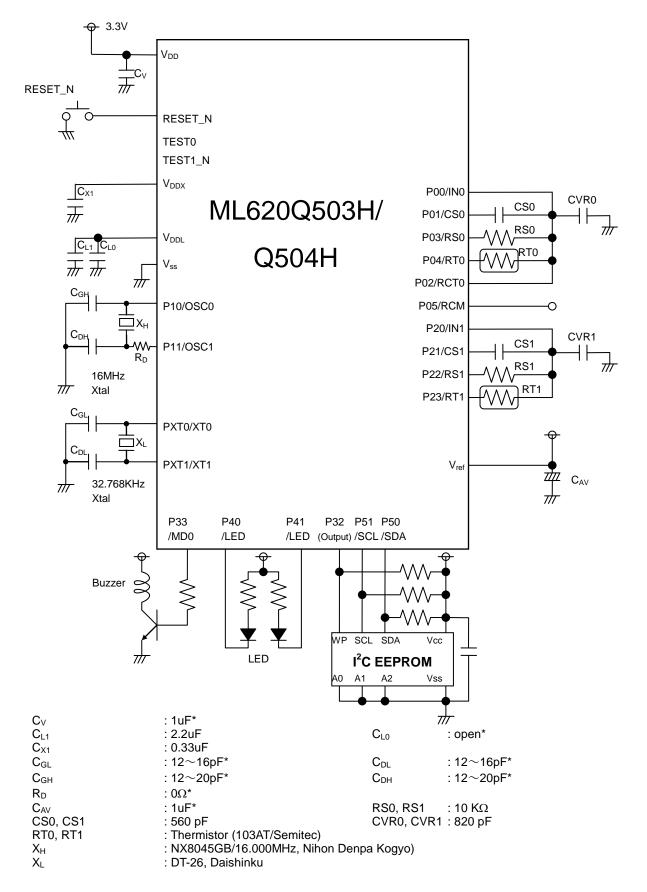

| 付録 D 応用回路例                                                                                                                |      |

| <u>改版履歴</u>                                                                                                               |      |

## 第1章 概要

#### 1. 概要

#### 1.1 特長

本 LSI は、16 ビット CPU nX-U16/100 を搭載し、SSIO、UART、I<sup>2</sup>C、電源電圧レベル検出回路、RC 発振式 AD コンバータ、逐次比較型 AD コンバータ等、多彩な周辺機能を集積した高性能 CMOS16 ビットマイクロコントローラです。

CPU nX-U16/100 は、3 段パイプラインアーキテクチャによる並列処理をすることで 1 命令 1 クロックの効率的な命令実行が可能です。また、プログラムメモリとして低電圧/低消費電力動作(読み出し時)を実現したフラッシュ ROM を搭載しており、バッテリー動作のアプリケーションに最適です。更に、ソフトウェアによる書き込み可能なデータフラッシュ・メモリ領域やソフトウェアからプログラム領域を書き換える機能を持ちます。

オンチップデバッグ機能を搭載しているため、基板実装状態でのソフトウェアのデバッグや書き換えも可能です。

#### • CPU

- RISC 方式 16 ビット CPU (CPU 名称: nX-U16/100)

- 一 命令体系:16ビット長命令

- 一命令セット:転送,算術演算,比較,論理演算,乗除算,ビット操作,ビット論理演算,ジャンプ,条件ジャンプ,コール・リターンスタック操作,算術シフトなど

- オンチップデバッグ機能を内蔵

- 一 最小命令実行時間

- 30.5us(@32.768kHz システムクロック)

- 62.5ns (@16MHz システムクロック)

#### ● 乗除算コプロセッサ

- 一 符号有り、無しの演算の設定が可能

- 乗算 16bit×16bit (演算時間 4 サイクル)

- 除算 32bit÷16bit (演算時間 8 サイクル)

- ― 除算 32bit÷32bit (演算時間 16 サイクル)

- 積和(非飽和型) 16bit×16bit+32bit (演算時間 4 サイクル)

- 積和(飽和型) 16bit×16bit+32bit (演算時間 4 サイクル)

#### ● 内部メモリ

- 一 ISP 機能対応(ソフトウェアでプログラムメモリを書き換え可能)

- ー メモリサイズ

| 製品名         | フラッシュン               | メモリ               | SRAM              |  |  |

|-------------|----------------------|-------------------|-------------------|--|--|

| <b>表</b> 四位 | プログラム領域 <sup>*</sup> | データ領域             | SKAIVI            |  |  |

| ML620Q503H  | 32K バイト(16K×16 ビット)  | 2K バイト(1K×16 ビット) | 2K バイト(1K×16 ビット) |  |  |

| ML620Q504H  | 64K バイト(32K×16 ビット)  | 2K バイト(1K×16 ビット) | 6K バイト(3K×16 ビット) |  |  |

<sup>\*:</sup> 使用できないテスト領域 1K バイトを含む

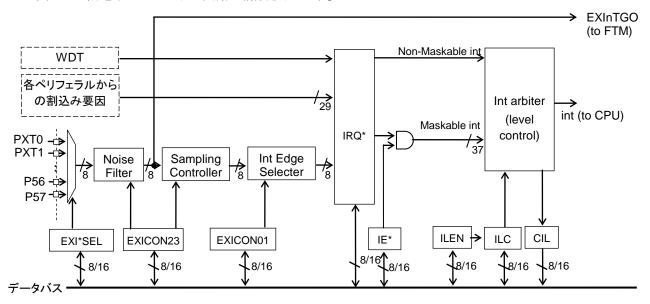

#### ● 割込みコントローラ(INTC)

- ノンマスカブル割込み1要因(内部要因:1)

- 一 マスカブル割込み 37 要因(内部要因:29、外部要因:8)

- ソフトウェア割込み(SWI)最大 64 要因

- 外部割込み、コンパレータはエッジの選択、サンプリング有無が選択可能

- 一 各割込みに対して、優先レベル(4レベル)の設定可能

#### ● タイムベースカウンタ(TBC)

— 低速タイムベースカウンタ×1ch

#### ● タイマ(TMR)

- 8 ビット×8ch(2ch 使用で 16 ビット構成可能)

- 一 ワンショットタイマモード機能

- 一 カウンタクロックに外部クロックを選択可能

- 多機能タイマ(FTM)

- 16 ビット×4ch

- オートリロードタイマモード/ワンショットタイマモード/PWM モード

- ソフトウェア/イベントトリガ(外部端子,他のタイマ)によるタイマスタート・ストップ機能

- 一 カウンタクロックに外部端子を選択可能

- キャプチャ機能(外部トリガ入力を利用してパルス幅などの測定が可能)

- 一 デッドタイム付き相補 PWM 出力、同期 PWM 出力

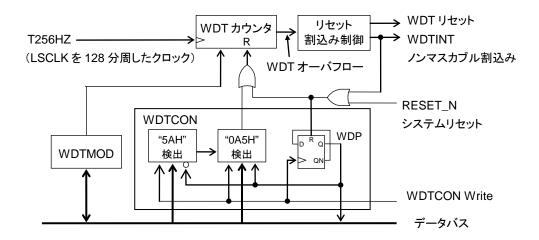

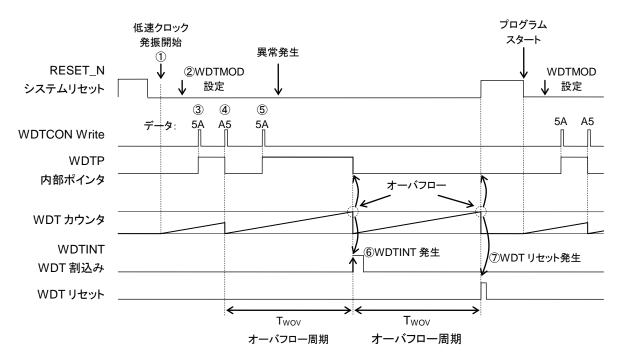

- ウォッチドッグタイマ(WDT)

- ノンマスカブル割込み、およびリセット (1回目のオーバフローで割込みを発生、2回目のオーバフローでリセットを発生)

- 一 フリーラン

- オーバフロー周期は、125ms、500ms、2s、8s から選択可能 (LSCLK=32.768kHz 時)

- 同期式シリアルポート(SSIOF/SSIO)

- 4ワード 送信/受信 FIFO 内蔵 ×1 ch, FIFO なし ×1 ch

- 一 マスタ/スレーブ選択可能

- 一 LSB/MSB ファースト選択可能

- 8ビット/16ビット長選択可能

- 一 クロックの位相及び極性を選択可能

- スレーブセレクト信号対応 (FIFO 内蔵タイプのみ)

- UART(UARTF/UART)

- 4 バイト 送信/受信 FIFO 内蔵 ×1 ch, FIFO なし ×1 ch

- 一 全二重通信対応

- 通信速度 2400~115200bps を設定可能

- プログラマブルインタフェース(データ長、パリティ、ストップビットの選択可能)

- $I^2C$  バスインタフェース( $I^2C$ )

- マスタ × 2 ch

- 標準モード(100kbit/s)、ファーストモード(400kbit/s)対応

- 汎用ポート(PORT)

- 一 入出力ポート×36ch, 入力ポート×2ch

- メロディドライバ(MELODY)

- 一 テンポ:15 種

- 音階:29 種(メロディ音周波数:508Hz~10.922kHz)

- 一 音長:63 種

- ブザー出力モード(出力モード4種、ブザー周波数8種、デューティ変更15レベル(ブザー周波数=4.096kHz 時は、7レベル))

- RC 発振型 A/D コンバータ(RC-ADC)

- 一 時分割 2ch 方式

- 24 ビットカウンタ

- 逐次比較型 A/D コンバータ(SA-ADC)

- 入力 12ch

- 一 分解能 12 ビット

- タイマによるスタート機能

- 一 静電容量タッチセンス機能

- アナログコンパレータ(CMP)

- 入力 2ch

- コモンモード入力電圧: 0.2V~V<sub>DD</sub>-0.2V

- 一 入力オフセット電圧: 30mV(max)

- 一 割込みはエッジの選択、サンプリング有無が選択可能

- 電圧レベル検出(VLS)機能

- 一 閾値電圧:13 値より選択

- 一 割込み発生、リセット発生選択可能

- 低電圧検出(LLD)機能

- 閾値電圧:1.8V±0.2V

- 一 リセット発生可能

- リセット

- RESET N 端子リセット

- パワーオン検出リセット

- 一 WDT オーバーフローによるリセット

- 一 電圧レベル検出(VLS)リセット

- 一 低電圧検出(LLD)リセット

- クロック

- 低速側クロック (本 LSI は、低速クロックは必須です)

- 一 水晶発振(32.768kHz)

- 一 外部クロック入力(30kHz~36kHz)

- 内蔵 RC 発振(32.768kHz)

- 一 高速側クロック

- 水晶/セラミック発振(16MHz)

- 一 外部クロック入力(2MHz~16MHz)

- 内蔵 RC 発振(16MHz)

- プワーマネジメント

- HALT モード: CPU の命令実行中断(周辺回路は動作状態)

- ― HALT-H モード: CPU の命令実行中断(周辺回路は動作状態で高速クロックを自動で停止)

- DEEP-HALT モード: CPU の命令実行中断(タイマ、LTBC など動作可能な超ローパワーモード)

- 一 STOP モード: 低速発振および高速発振の停止 (CPU および周辺回路は動作を停止)

- 一 クロックギア:ソフトウェアにより高速システムクロックの周波数を変更可能(発振クロックの 1/1、1/2、1/4、1/8、1/16、1/32)

- ブロック制御機能:使わない機能ブロック回路の動作をパワーダウン(レジスタリセット&クロック停止)

第1章 概要

#### ● 出荷形態

- ― チップ(ダイ) \*パッドレイアウト情報につきましては、弊社担当営業までお問い合わせください。

- 48 ピン プラスチック TQFP

トレイ

ML620Q503H-xxxTBWAAL ML620Q504H-xxxTBWAAL

テープ&リール

ML620Q503H-xxxTBWABL ML620Q504H-xxxTBWABL

#### ● 動作保証範囲

— 動作温度(周囲): Ta=-40℃~85℃

— 動作電圧:V<sub>DD</sub>=1.8V~5.5V

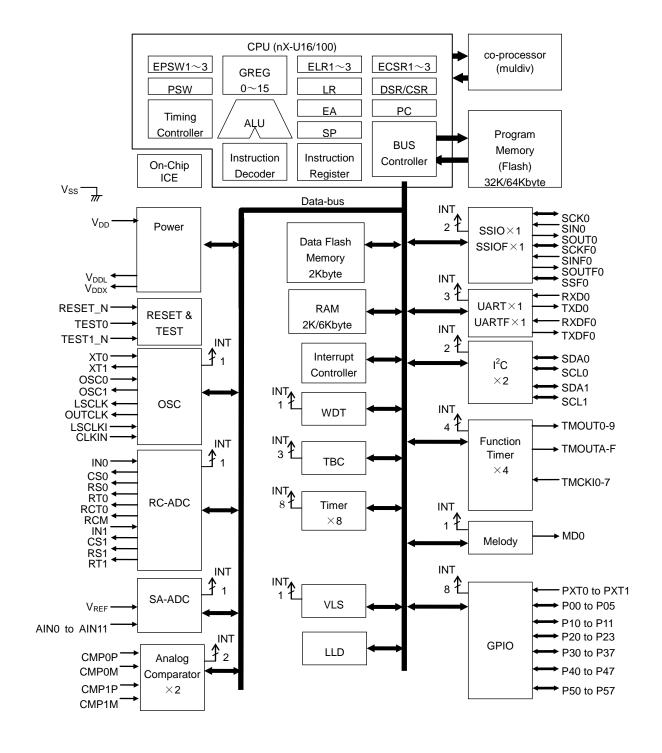

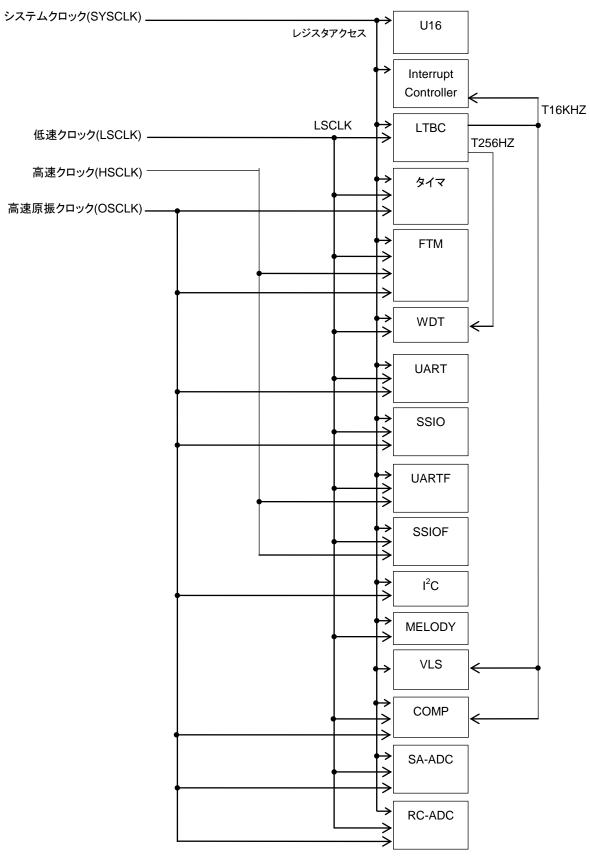

#### 1.2 機能ブロック構成

#### 1.2.1 ML620Q503H/Q504H ブロック図

図 1-1 ML620Q503H/Q504H ブロック図

#### 1.3 端子

#### 1.3.1 端子配置

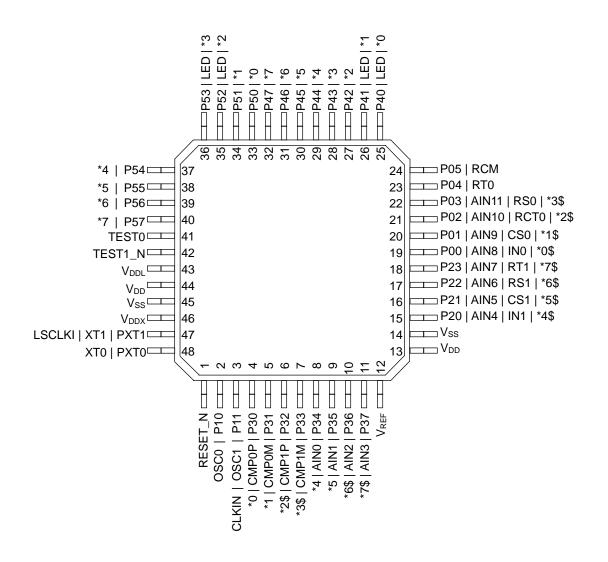

#### 1.3.1.1 ML620Q503H/Q504H TQFP パッケージの端子配置図

外部割込み入力端子(EXI)は P00-P05,PXT0-1,P20-P57 に割付可能です。

\*0~\*7 は下記の機能群をもちます。但し、末尾に"\$"がつくものは一部機能がありません。詳細は、端子一覧を参照して下さい。

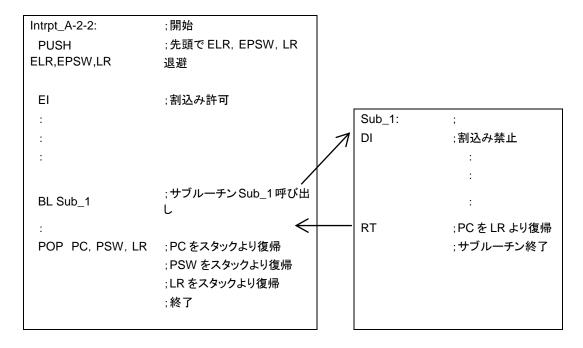

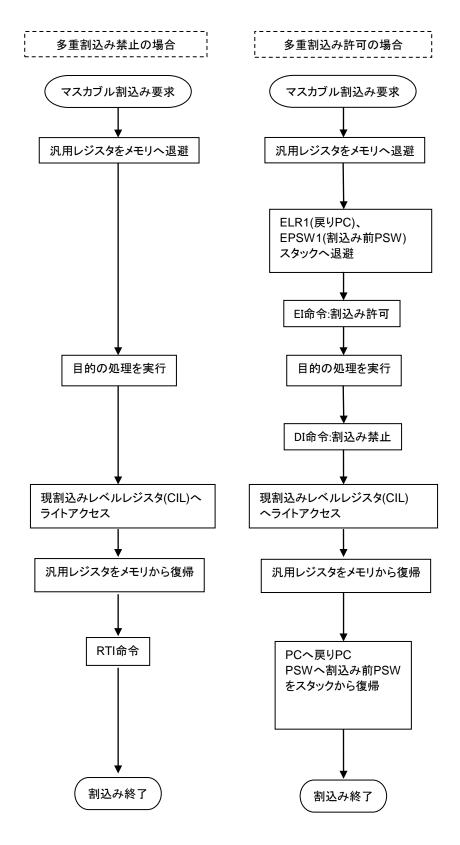

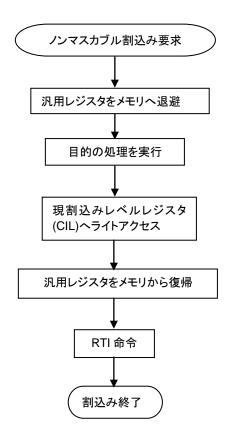

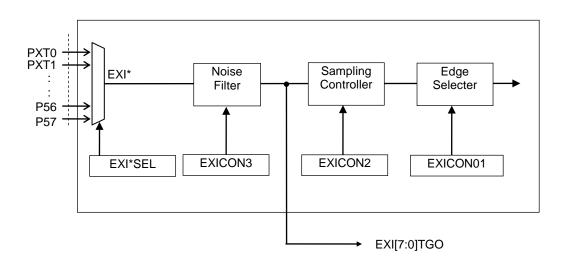

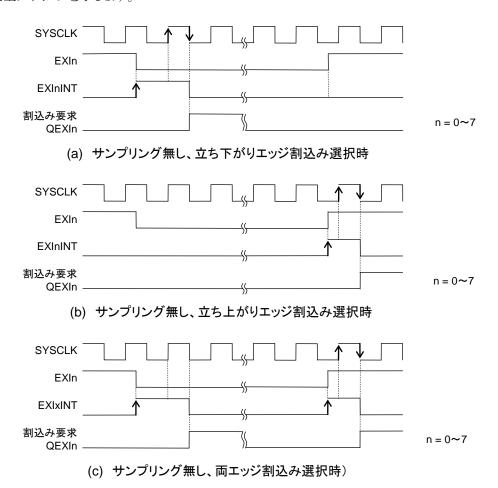

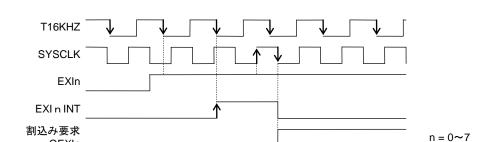

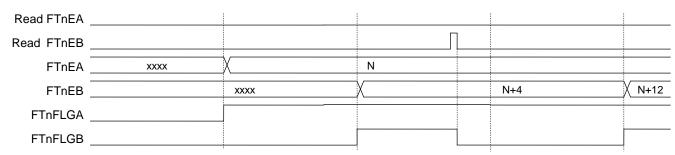

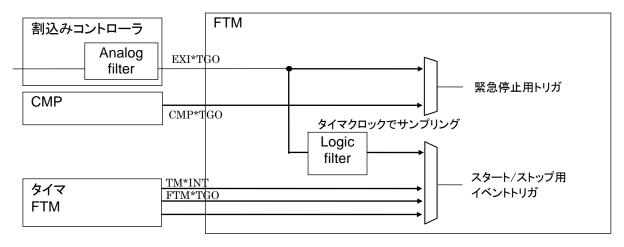

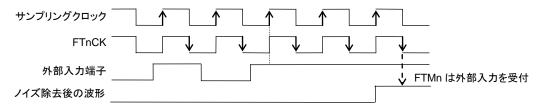

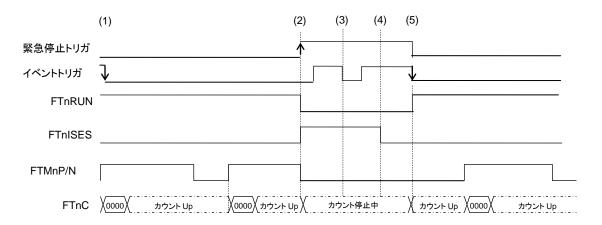

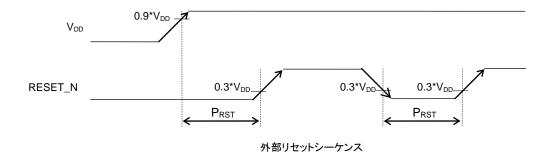

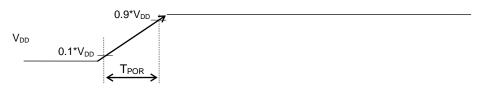

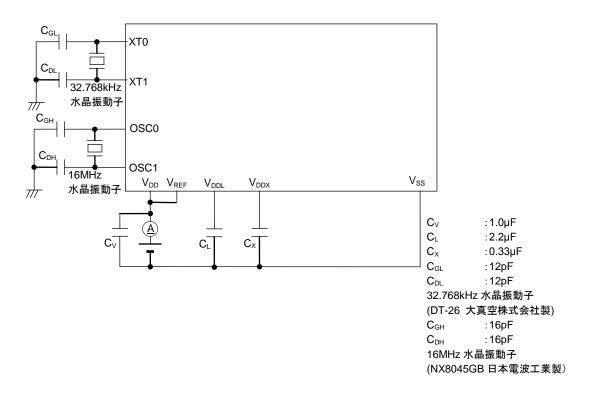

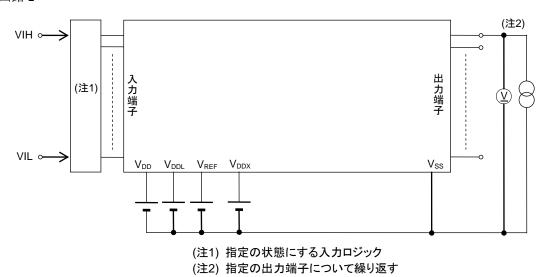

\*2 : SCK0, TMOUT ,TMCKI \*3 : MD0, TMOUT , TMCKI \*7 : OUTCLK, SSF0, TMOUT, TMCKI